Electroplating innovation enables ultrafine indium bonding

Flip-chip bonding is essential to hybridization, the process of

combining die from differing technologies into a high performance module

such as the hybrid pixel detectors found in LiDAR and other imaging

applications. The tin solders once used in flip-chip bonding are being

replaced by lead-free alternatives including indium. However, creating

the indium ‘bumps’ essential to forming bonds is challenging using

conventional approaches. The experts at ClassOne Technology believe a

new electroplating process solves the indium bump corundum.

BY

FARZANEH SHARIFI AND BRANDEN BATES, CLASSONE TECHNOLOGY; ELIE NAJJAR,

WENBO SHAO, PHD; ERIK YAKOBSON, PHD; AND BRIAN GOKEY, MACDERMID ALPHA

ELECTRONIC SOLUTIONS

HYBRID PIXEL DETECTORS are widely used for imaging applications ranging from high-energy physics to military, environmental and medical. Hybrid pixel detectors combine a pixel sensor chip with a readout integrated circuit (ROIC), which allows electronic access to every pixel in the detector. Pixel sensors are made of high-resistivity silicon, while low-resistivity material is required for the ROIC. Hybridization allows each one to be manufactured independently and then later coupled together through a process called flip-chip or bump bonding.

Flip-chip bonding creates a contact that provides high input/output (I/O) density and a short interconnect distance between the sensor pixel and the ROIC, enabling high device performance. During flip-chip bonding, the solder bumps are melted to form this connection. The pixels in a hybrid detector are placed in an array with less than 100-micron (mm) distance, or pitch, between them. This high connection density requires finer, more precise bumps and a very high-yield flip-chip process that ensures each pixel is connected to the IC.

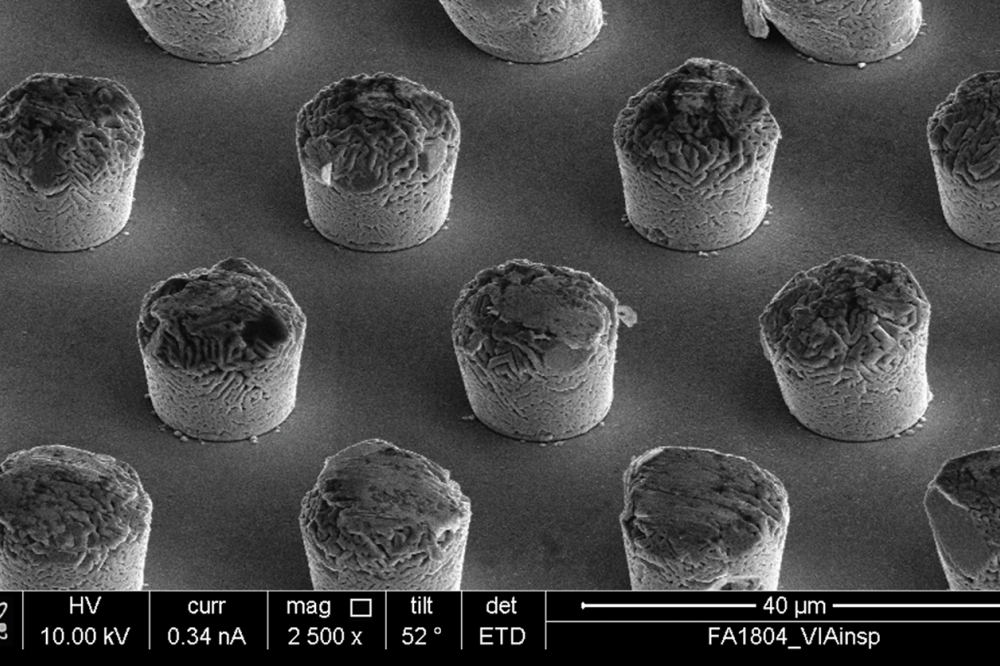

Figure 1a & 1b: Confocal microscopy data (a) topography map of indium features (b) profilometry. The bumps were observed using a scanning electron microscope (SEM) as shown in Figure 2.

Flip-chip evolution

Conventional flip-chip assembly was first achieved using lead-based solder bumps, but those materials have had to be revisited due to the worldwide banning of lead in electronic products due to its toxicity. However, lead-free alternatives such as pure tin or various tin-based lead-free alloys, e.g., SnAgCu (tin-silver-copper, or SAC), also face challenges with pixel detectors, so a viable alternative is a necessity.

Since the readout chips and sensor chips are made of different materials, a low-temperature fabrication process is necessary to reduce the thermal impact on the sensor chips due to a mismatch in coefficient of thermal expansion (CTE). Additionally, the sensors can face environmental extremes, from harsh radiation to cryogenic temperatures. Together, all these challenges require a new solder material with specific characteristics. We propose indium as one such preferred candidate.

Why indium?

Indium is a soft metal (softer than lead) with a low melting point (156oC) that is highly malleable and ductile and retains these properties at very low temperatures, i.e., down to absolute zero (-273oC). This makes indium ideal for cryogenic and vacuum applications.

In terms of chemical properties, indium reacts with oxygen only at higher temperatures, doesn’t dissolve in acids, has good adhesion to other metals, and has the ability to wet glass. Its good electrical conductivity, ductility, and low-temperature stability make it an excellent candidate for use in hybrid pixel detectors.

Older approaches

Indium bumps were previously fabricated via thermal evaporation, or sputtering, which yields highly uniform bumps with good bump structure control. However, this method cannot produce small bumps (higher aspect ratio) with a smaller pitch that’s suitable for the semiconductor industry’s current needs.

Moreover, indium sputtering requires expensive evaporation equipment, is limited to materials with high vapor pressure, requires a complicated fabrication process, isn’t well suited to larger wafer sizes because of mask-to-wafer mismatch, is less environmentally safe as it creates more pollution, and is only viable for small-scale production.

In contrast, electroplating bumps with a high aspect ratio, at low cost, and with a simple fabrication process is achievable, especially for mass production. But conventional electroplating needs optimization, as non-uniform bumps cause failures in the fabrication process and reduce the hybrid chip’s reliability. Evaporation of indium bumps for ultrafine pitch is difficult and time-consuming. Moreover, the waste of material on the photoresist mask renders the process non-cost-effective, and the smallest pitch size achievable through this approach is 30 mm.

Figure 2. Scanning electron microscope images of indium bump

Electroplating challenges

Electroplating faces multiple challenges when utilized to create flip-chip bonding bumps: it must achieve the required uniformity and consistency of plated bumps, with ultrafine pitch, at wafer-scale and at high yield. It becomes even more challenging as the pitch shrinks and the number of bumps increases.

As wafer features shrink in size, bump sizes will decrease from 50 to 15 µm, with pitch sizes decreasing from 100 to 25 µm. Our goal was to demonstrate the capability of electroplating to generate high-density indium bumps with high quality and yield. Our work proved that electroplating smaller bump sizes with reduced pitch is achievable with the proper tool and material sets.

Process steps

Indium bumps are electroplated after under-bump metallization (UBM) is deposited on the silicon wafer. For the UBM, a barrier and adhesive layer such as titanium is needed, followed by an indium-wettable layer such as nickel or gold since nickel tends to oxidize quickly. The height of the indium balls is defined by the volume of the indium and the diameter of the wettable UBM pad. In our test, we used copper for the outer layer of the UBM. At temperatures around 125oC, some trivial amounts of indium form intermetallic phases with copper; then, for higher temperatures, a barrier metal such as nickel-gold or nickel-copper should be used.

After removing the top UBM layer (copper in our tests), wafers are heated to a temperature at which the electroplated indium bumps form spheres due to the surface tension. The purpose of reflow is to increase bump height by reshaping the indium into a sphere and to help the flip-chip bonding alignment.

The copper seed layer is etched away with nitric acid mixed with water before reflowing. Titanium, a non-wettable material, was used to prevent the spread of indium across the surface during reflow. Indium has good adhesion to the top layer of the UBM (copper) but not the surrounding material (Ti).

Reflow must be performed in an oxygen-free environment, i.e., a controlled atmosphere in an oven; otherwise, indium oxide would form, impeding indium bump formation. In our study, the bumps were reflowed on a hot plate at a temperature of around 200oC, with nitrogen gas blowing on the surface.

Following reflow, the pixel sensor and ROIC are mated via low pressure at room temperature. In an industry application, a second reflow is performed following the flip-chip procedure to achieve self-alignment with the surface tension of the molten indium, as well as high strength.

Factors that affect the quality and yield of the bumps include uneven UBM, the etching process, reflowing temperature profile, and cleaning after reflowing. Accurate alignment of the photoresists during the lithography process is critical to achieving good-quality bumps, but not as much as in the evaporation process. Current distribution and mass transport during the electroplating process are the main factors in electroplating that determine indium deposit growth and influence the bumps’ shape evolution.

Experimental approach

In this work, we attempted to electroplate ultra-fine-pitch indium bumps (features with 10 µm size and pixel pitch of 5 µm and 7.5 µm) with a very uniform height. We used a 6-inch silicon wafer as the substrate with a copper seed layer and 17 µm of thick photoresist developed to form the required pattern. Strict control of photoresist thickness is required to assure good bump profile. We used a vacuum prewet process for bubble removal and prewetting small patterns, and selected a pure indium plate for the anode, assuring 100% anode efficiency.

Indium bump electroplating was carried out through direct current (DC), pulse, and pulse reverse current waveforms. The average current densities of pulse and pulse reverse current were kept the same as the DC condition to enable direct comparison.

Role of the electrolyte

Various chemistries have been used for indium plating to date. Resist damage, due to hydrogen evolution, large grains and nodules, is the primary defect resulting from conventional indium plating electrolytes. MacDermid Alpha Electronics Solutions has developed an indium electrolyte to overcome these killer defects.

Novafab IN-100 is an acid electrolyte system created for low-temperature, lead-free solder interconnect. This proprietary electrolyte was formulated to deposit indium metal at high efficiency and, unlike conventional indium plating baths, does not produce hydrogen evolution due to its innovative chemical composition.

During electroplating, the pH at the metal-solution interface is kept stable, eliminating drastic pH increases that may result in photoresist lift and damage. Thus, Novafab IN-100 is suitable for photoresist-patterned wafer plating because of its intrinsic photoresist compatibility. It produces a fine-grained, nodule-free matte deposit with >99.5% pure Indium and exhibits superior adhesion. The solution is fully analyzable and is compatible with both soluble and insoluble anode systems.

Conclusion

The height of the plated bumps was measured by using a confocal microscope, as shown in Figure 1. To remove the effect of the non-optimized reflowing process, height measurements were taken after electroplating and before the reflow process. Among the three waveforms we used, pulse plating with a high ratio of on-time to off-time yielded the best results. Measuring the height of the bumps, we were able to get uniformity of less than 10 percent across the wafer.

An indium oxide layer did form on the surface of the bumps in our demonstration process, so we weren’t able to obtain a perfectly shaped sphere after reflowing, but it was observed that the bumps began to be rounded and form a sphere.

The properties of the indium electrolyte combined with the flip-chip process performed on ClassOne’s Solstice single-wafer platform illustrated a viable approach to using indium for flip-chip electroplating processes.