Keysight enable system-on-a-chip makers with new test solutions

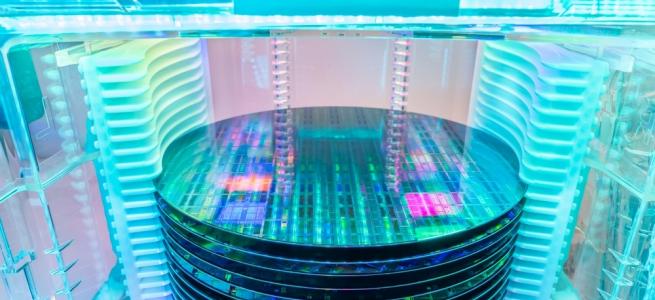

Keysight Technologies, a technology company that delivers advanced design and validation solutions to help accelerate innovation to connect and secure the world, has announced that the company’s new 224G Ethernet test solutions enables system-on-a-chip (SoC) makers to validate next generation electrical interface technology, accelerating 1.6 terabit per second (1.6T) transceiver design and pathfinding.

5G, artificial intelligence (AI) and internet of things

(IoT) applications are driving growth in data traffic, creating unprecedented

bandwidth demands in networks and data centers. High-speed digital interfaces

that support 224 Gbps per lane data connection speeds offer increased

bandwidths and underpin 1.6 terabit per second (1.6T) high-speed interconnect

technology. Improved data throughput and efficiency in data center networks

also reduce power consumption and cost. Keysight is the only provider of bit

error ratio tester (BERT) solutions capable of generating and analyzing 224

gigabit per second (224 Gbps) signals.

“Keysight is pleased to enable Synopsys, and other semiconductor makers, capture early market opportunities associated with the transition from 800 gigabit per second (800G) to 1.6T,” said Dr. Joachim Peerlings, vice president of Network and Data Center Solutions at Keysight Technologies. “Keysight’s unique portfolio of high-speed digital interface test solutions enable Synopsys to validate the performance of 224G IP designs accelerating 1.6T design and pathfinding.”

The M8050A BERT offers users a unique 224 Gbps test solution for electrical design and validation of transceiver SoCs used in data centers and networks for transferring large amounts of data at high speeds. Keysight’s M8050A BERT provides signal integrity that enables accurate characterization of receivers used in next-generation data center networks and server interfaces. Synopsys used Keysight’s M8050A BERT, M8199 Arbitrary Waveform Generator (AWG) and Infiniium UXR-Series Oscilloscope to develop and validate 224G serializer/deserializer (SerDes) IP designs.

“High-performance computing systems depend on high-speed, low-latency interfaces to process massive amounts of data with minimal power,” said John Koeter, senior vice president of marketing and strategy for the Solutions Group at Synopsys. “As a leading provider of high-speed Ethernet IP solutions, Synopsys utilizes Keysight’s comprehensive digital interface test solutions to validate the performance of the PHY IP, enabling designers to meet their design and system-level requirements for high-performance computing, networking and AI SoCs.”

At the European Conference on Optical Communication (ECOC) 2022 in Basel, Switzerland, Keysight and Synopsys will demonstrate the industry’s first common electrical interface (CEI) SoC supporting 224Gbps. Exhibition visitors can view the demonstration at the booth hosted by the Optical Internetworking Forum (OIF), an industry organization that promotes the development and deployment of interoperable networking solutions and services for optical networking products, network processing elements and component technologies.