UMC and Cadence collaborate

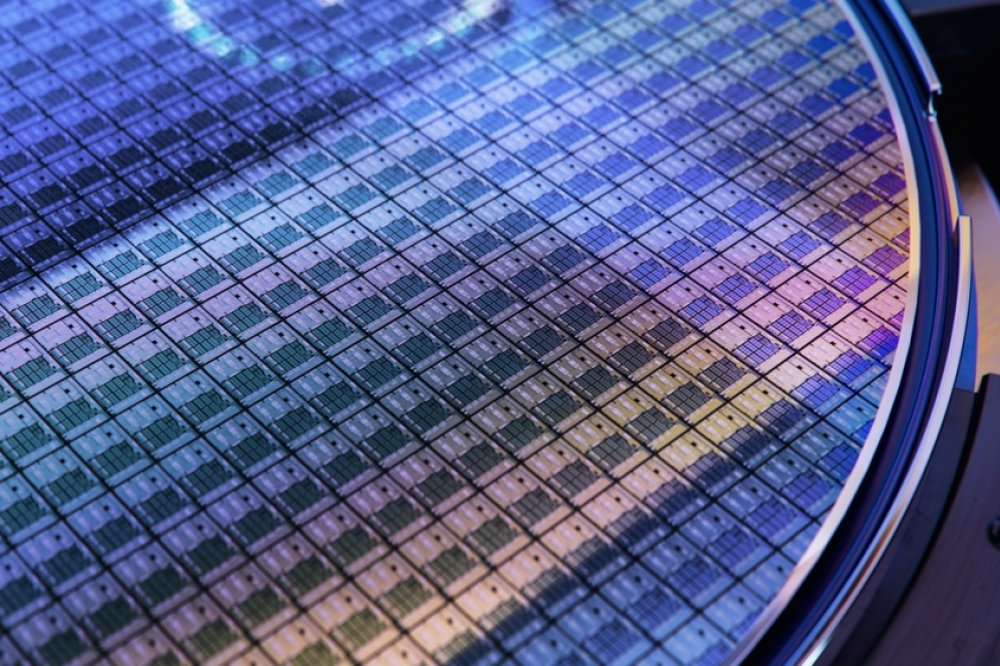

The Cadence 3D-IC reference flow, featuring the Integrity 3D-IC Platform, has been certified for UMC’s chip stacking technologies, enabling faster time to market.

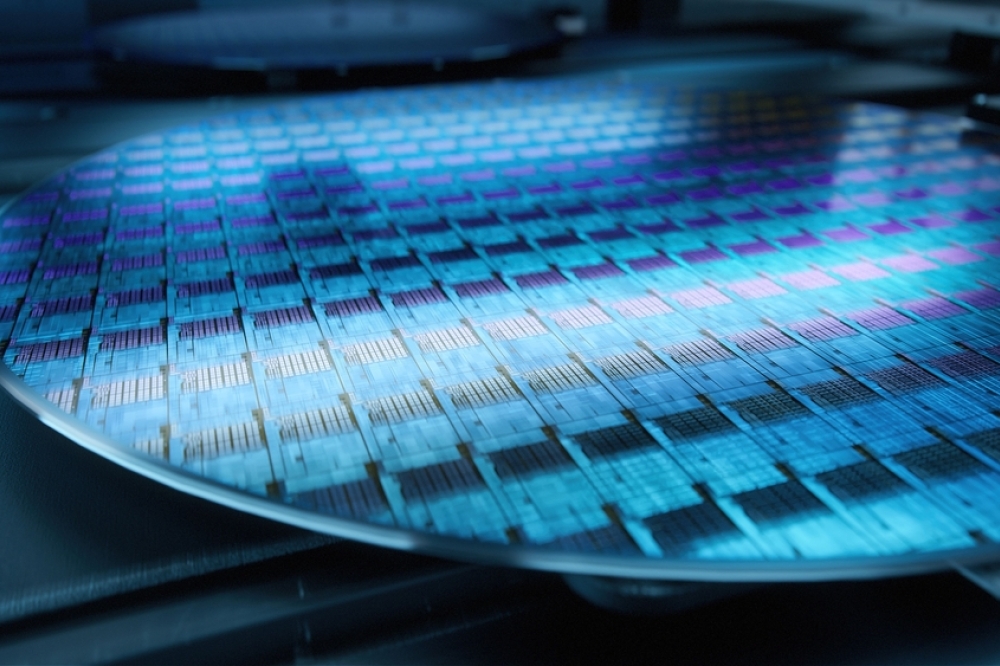

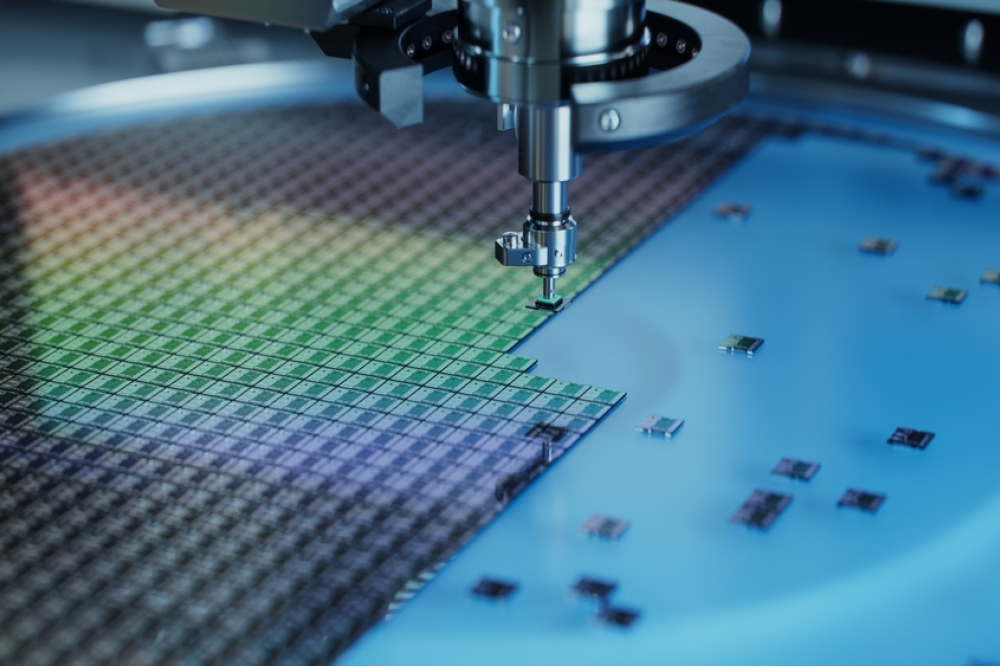

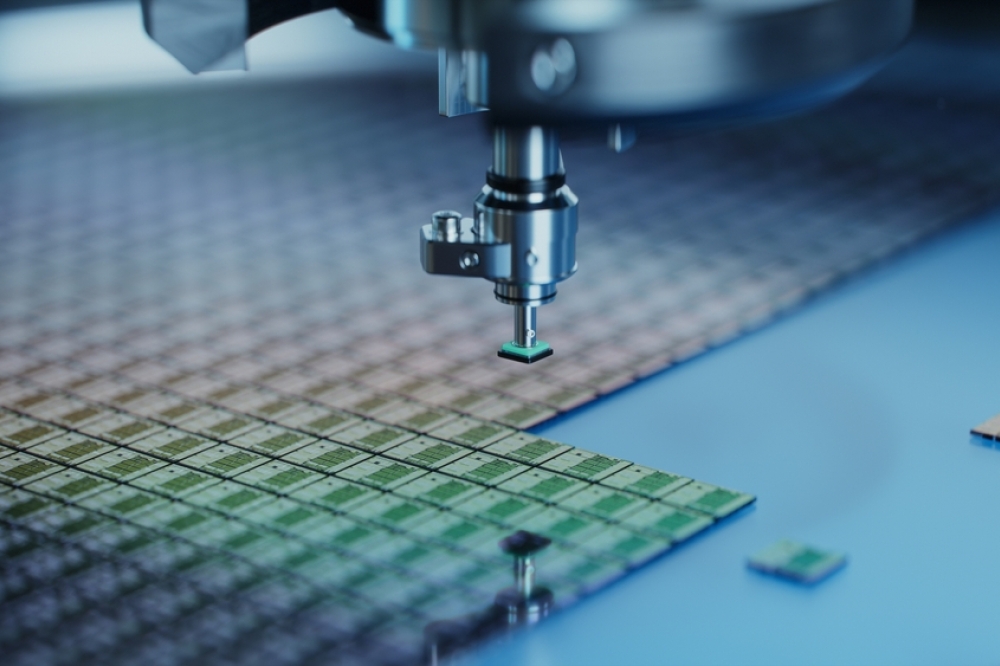

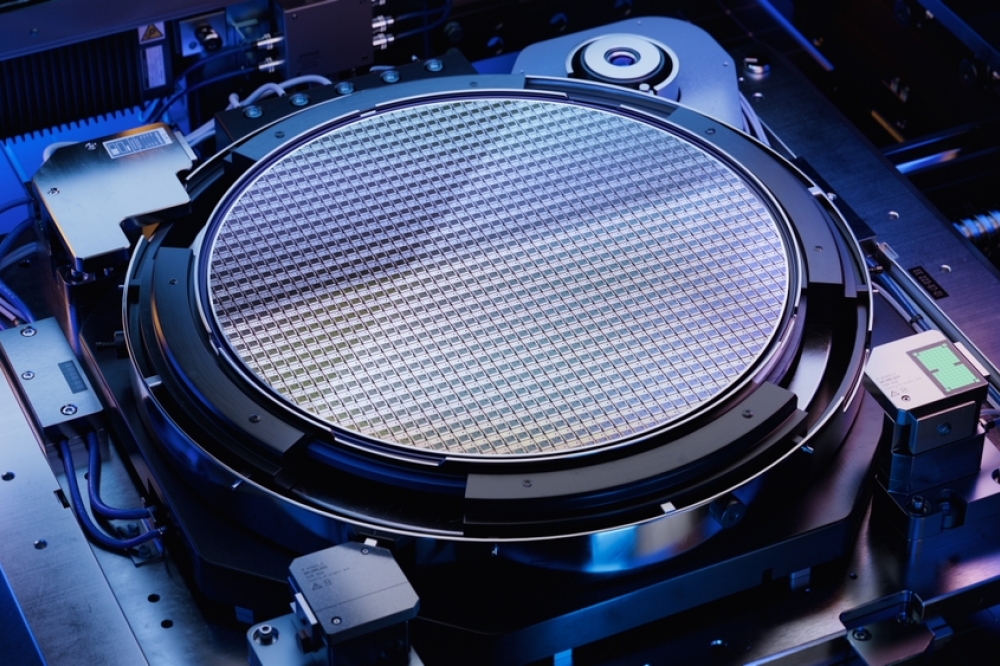

UMC’s hybrid bonding solutions are now ready to support the integration across a broad range of technology nodes that are suitable for edge AI, image processing, and wireless communication applications. Using UMC’s 40nm low power (40LP) process as a wafer-on-wafer stacking demonstration, the two companies collaborated to validate key 3D-IC features in this design flow, including system planning and intelligent bump creation with Cadence’s Integrity 3D-IC platform, said to be the industry’s first comprehensive solution that integrates system planning, chip and packaging implementation, and system analysis in a single platform.

“Interest in 3D-IC solutions has increased notably in the past year as our customers seek ways to boost design performance without sacrificing area or cost,” said Osbert Cheng, vice president of device technology development & design support at UMC. “Cost-effectiveness and design reliability are the pillars of UMC’s hybrid bonding technologies, and this collaboration with Cadence provides mutual customers with both, helping them reap the benefits of 3D structures while also accelerating the time needed to complete their integrated designs.”

"With increasing design complexity for IoT, AI, and 5G applications, wafer-on-wafer technology automation is increasingly important for chip designers,” said Don Chan, vice president, R&D in the Digital & Signoff Group at Cadence. “The Cadence 3D-IC flow with the Integrity 3D-IC platform is optimized for use on UMC’s hybrid bonding technologies, providing customers with a comprehensive design, verification and implementation solution that enables them to create and verify innovative 3D-IC designs with confidence while accelerating time to market.”

The reference flow, featuring Cadence’s Integrity 3D-IC Platform, is built around a high-capacity, multi-technology hierarchical database. The platform offers design planning, implementation and analysis of full 3D designs within a single, unified cockpit. Multiple chiplets in a 3D stack can be designed and analyzed together through integrated early analysis for thermal, power and static timing analysis. The reference flow also enables system-level layout versus schematic (LVS) checking to connectivity accuracy, electric rule-checking (ERC) for coverage and alignment checking, and thermal analysis for heat distribution in a 3D stacked-die design structure.