Co-packaged Optics: all eyes on high-performance computing

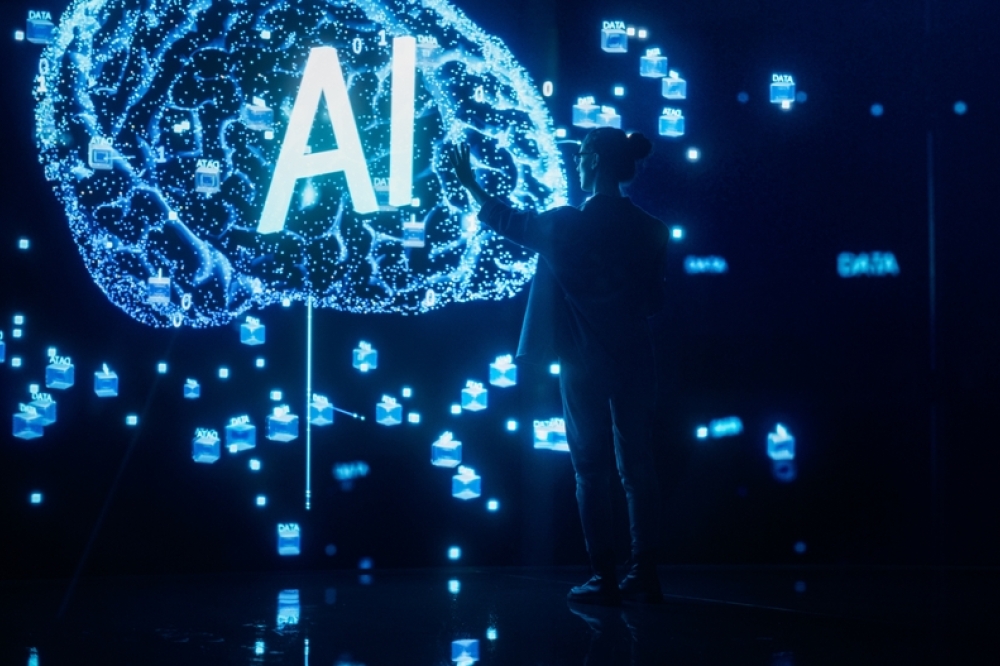

AI bottlenecks drive the adoption of optical interconnects for next-generation HPC systems.

Revenue generated by the CPO market reached around US$38 million in 2022 and is expected to reach US$2.6 billion in 2033, at a 46% CAGR for 2022-2033. According to Yole Intelligence, part of Yole Group, projections of rapidly growing training dataset sizes show that data will become the main bottleneck for scaling ML models, and as a result, a slowdown in AI progress might be observed. Using optical I/O in ML hardware can help to solve the issues related to explosive data growth. To accelerate data movement in AI/ML gear is the main driver for adopting optical interconnects for next-generation HPC systems.

In this context, Yole Intelligence releases its Photonics & Lighting report, Co-packaged Optics for Datacenter 2023. In this report, the company – part of Yole Group – provides the context of why DC operators explore CPO technology, gives market forecasts split by technology architectures, and reviews the industry and the potential impact on the supply chain. It also examines technological approaches for CPO and discusses CPO challenges. In addition, this study reviews the global challenge and focuses on the POWER / ENERGY aspect.

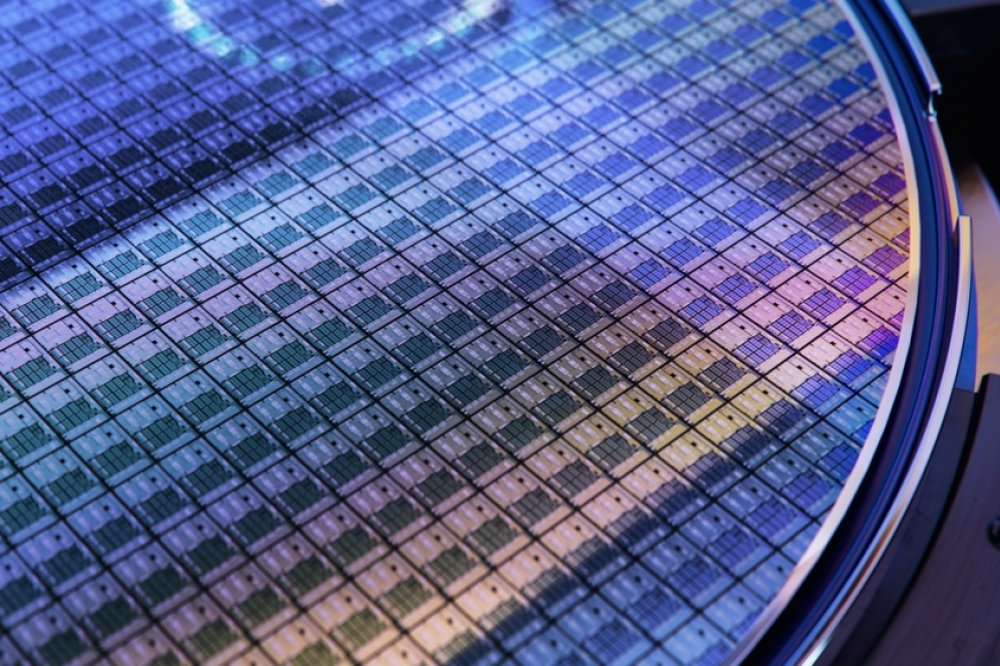

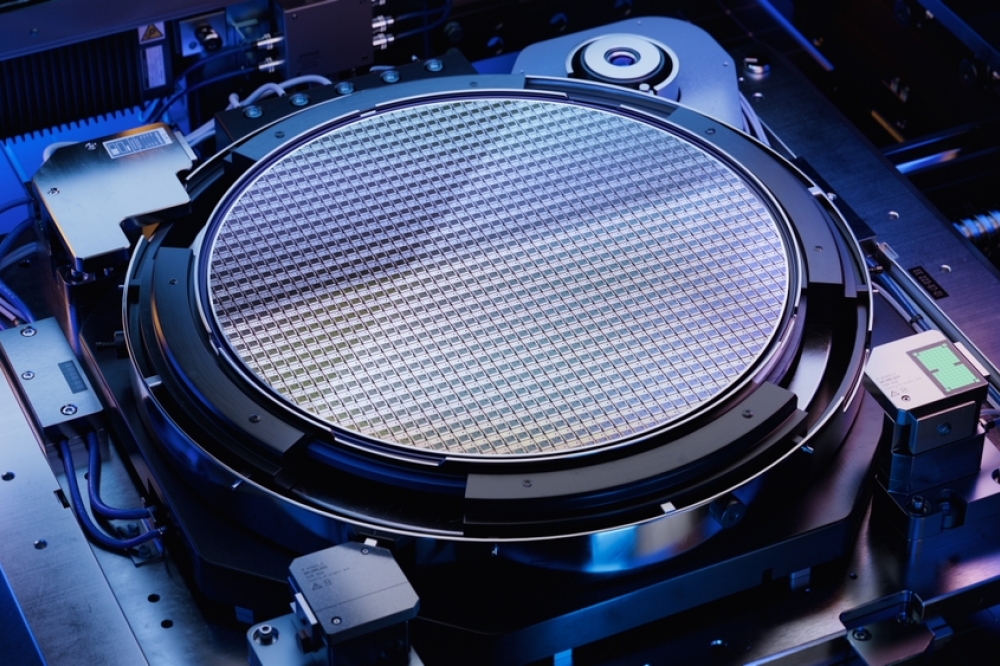

Optics are coming closer and closer to the chipset. Bringing in data using light to the point where it is centrally processed is one of the main goals of architecture designers. This trend started a decade ago with proprietary designs for optical assemblies mounted on PCBs . The idea of these EOIs has continued in the COBO , which has developed specifications to permit the use of board-mounted optical modules in the manufacturing of networking equipment. CPO is an innovative approach that brings the optics and the switch ASIC very close together. Since it is challenging with today’s technology to surround the 50T switch chip with 16 3.2Tbps optical modules, NPO tackles this by using a high-performance PCB substrate – an interposer – that sits on the host board, in contrast to CPO, where the modules surround the chip on a multi-chip module substrate. The NPO interposer is more spacious, making the signal routing between the chip and optical modules easier while still meeting signal integrity requirements. In contrast, CPO confines the modules and host ASIC much closer to each other with lower channel loss and power consumption.

As a result, new very-short-reach optical interconnects have emerged for HPC and its new disaggregated architecture. Disaggregated design distinguishes the compute, memory, and storage components found on a server card and pools them separately. Using advanced in-package optical I/O technology to interconnect xPUs , specifically CPUs , DPUs , GPUs , FPGAs , and ASICs, with memory and storage can help to achieve the necessary transmission speeds and bandwidths.