MoS Rajeev Chandrasekhar launches 3rd Semicon India Future DESIGN Road show at IIT Delhi

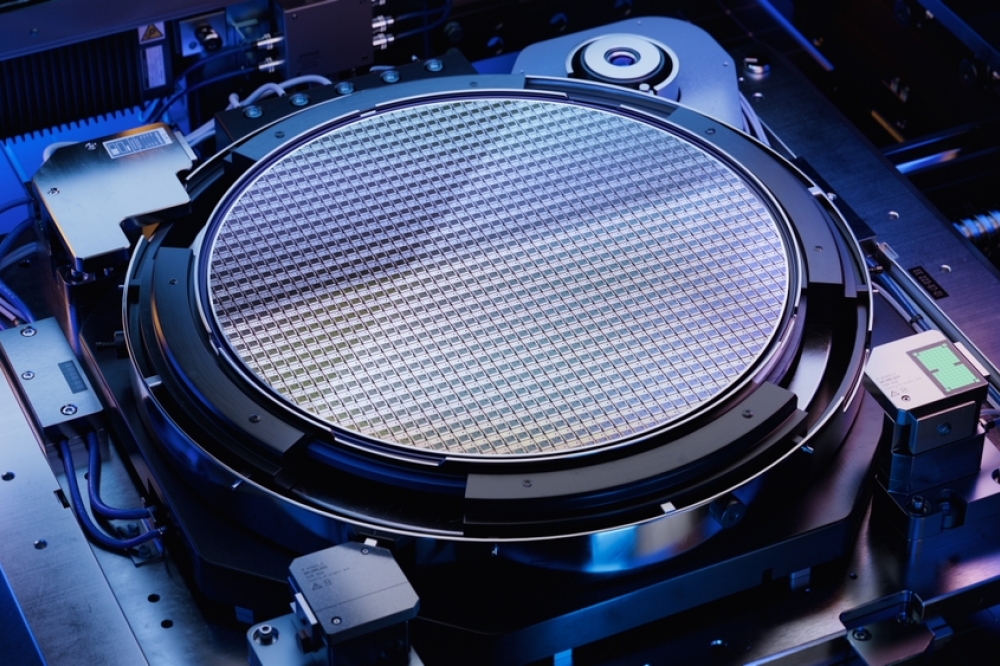

Union Minister of State for Electronics and Information Technology Shri Rajeev Chandrasekhar recently launched the 3rd Semicon India Future Design roadshow at IIT Delhi, with an aim to encourage innovation, facilitate investment and catalyse the Startups ecosystem in the semiconductor design and manufacturing space.

Speaking on the occasion, the Minister said, “The primary objective of this initiative is to attract investments from across the world and help build a vibrant semiconductor design and manufacturing ecosystem. PM Modi ji has announced Rs 76,000 crores as outlay for semiconductor sector to fulfil the vision of AtmaNirbhar Bharat. Already there are 27-28 semicon startups and the number will soon go up to 100, with the Government’s policy support.”

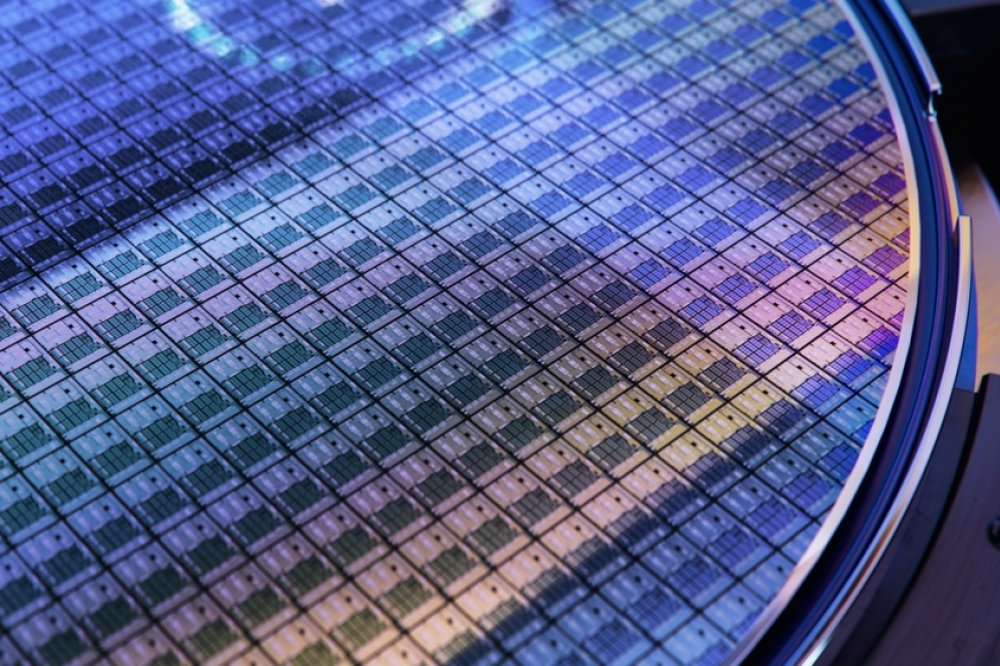

A slew of measures for the semiconductor sector have been put in place by the Government, he said. These include setting up an Indian Semiconductor research center (ISRC) that will work in collaboration with top institutions like the IITs for coming up with cutting edge semiconductor research, modernisation of Semiconductor Laboratory (SCL) implementation of the VLSI/ semiconductor curriculum that will deliver a talent pool of 85,000 who will create innovative designs and solutions.

The digital economy has now expanded from one being centred around IT/ITES to one that covers entire spectrum of Technology - Deep Tech, AI, Space, and Semiconductors. The Government is working in collaboration with industry, startups and academia to transform India from a consumer of technology to producer of technology, and for achieving our $1Trillion digital economy goal, the Minister emphasised.

During the roadshow, global semiconductor leaders like Mr Hidetoshi Shibata, President and CEO of Renesas Technology and Dr Vivek Lall, Chief Executive of General Atomics also shared their vision and expressed interest in collaboration with Indian startups.

“India is a critical part of Renesas’ business. There are plenty of opportunities for collaboration. If you have an opportunity, why not think of Renesas. Let’s design the Future together with Renesas,” said Mr Shibata, the Japanese chip maker.

IIT Delhi Director Rangan Banerjee and a large number of industry leaders, startups and members of the academia were present at the launch event. The 3rd Semicon India future design roadshow is part of a series of roadshows organised by the Ministry of Electronics and Information Technology across the country.

During the 3rd Roadshow, announcement on following futureDESIGN Start-ups (viz. Morphing Machines and Netrasemi) approved under the Design Linked Incentive (DLI) Scheme was made with a believe that the next unicorn will be from fabless chip design area -

Morphing machines is focusing on a dynamic runtime reconfigurable RISC-V many cores accelerator, with near ASIC performance across diverse domains & heterogeneous applications, all on the same homogeneous fabric.

Netrasemi is providing edge AI chipsets, platforms enabling smart vision and domain specific SoC solutions with advanced AI/ML and hardware acceleration capabilities.

Earlier during the 2nd Roadshow, announcement on following futureDESIGN Start-ups approved under the DLI Scheme was made-

Vervesemi Microelectronics is having expertise in reconfigurable analog and high-performance ADC. Vervesemi proposes to develop mixed-signal MCU Integrated Circuit.

Fermionic Design is developing Beamformer Integrated Circuits (IC) for 5G, SatNav, Industrial small-cell-arrays.

DV2JS Innovation is developing CMOS Image Sensor for Security, Surveillance, Automobile Cameras.

Sequoia Capital India pledged investment support to two DIR-V startups - InCore Semiconductors and Mindgrove Technologies. This augmented the vision of Shri Rajeev Chandrasekhar, Hon’ble Minister of State on DIR-V announced in April’ 2022 that DIR-V will see partnerships between Startups, Academia & Global Majors, and India will prove to be a RISC-V Talent Hub for World.

As part of the DIR-V program, C-DAC has successfully completed the design and development of the VEGA series of microprocessors comprising of 32/64-bit Single/Dual/Quad Core processors based on RISC-V ISA. A development platform based on THEAJS32 ASIC, named ARIES has been developed comprising of four different developer's kits viz. ARIES V2, ARIES Micro, ARIES IoT and ARIES V3.

The MeitY has set up ChipIN Centre at C-DAC Bangalore to dedicate its services to semiconductor design community of the country. The facility acts as one-stop centre to provide semiconductor design tools, fab access, virtual prototyping hardware lab access to fabless chip designers from Startups and Academia. The MoU s exchanged between C-DAC Bangalore and Ansys to nurture chip design using Ansys EDA tools hosted at ChipIN Centre.

Renesas Electronics Corporation, a premier supplier of advanced semiconductor solutions, introduced an NB-IoT (Narrowband Internet of Things) chipset specifically for the Indian market. The new chipset also can be used in asset tracking, lighting, security and numerous other applications.