New centre for semiconductor research in Dresden

With the establishment of the Center for Advanced CMOS &

Heterointegration Saxony, the Fraunhofer Institute for Photonic

Microsystems IPMS and the “All Silicon System Integration Dresden -

ASSID “ branch of Fraunhofer IZM are pooling their expertise in

semiconductor research.

BY MARTIN LANDGRAF, BUSINESS

DEVELOPMENT, KONRAD SEIDEL, GROUP LEADER EMERGING MEMORIES, AND ROBERT

KRAUSE, PROJECT MANAGER AND PROCESS ENGINEER, AT FRAUNHOFER IPMS.

With the establishment of the Center for Advanced CMOS & Heterointegration Saxony, the Fraunhofer Institute for Photonic Microsystems IPMS and the “All Silicon System Integration Dresden - ASSID “ branch of Fraunhofer IZM are pooling their expertise in semiconductor research.

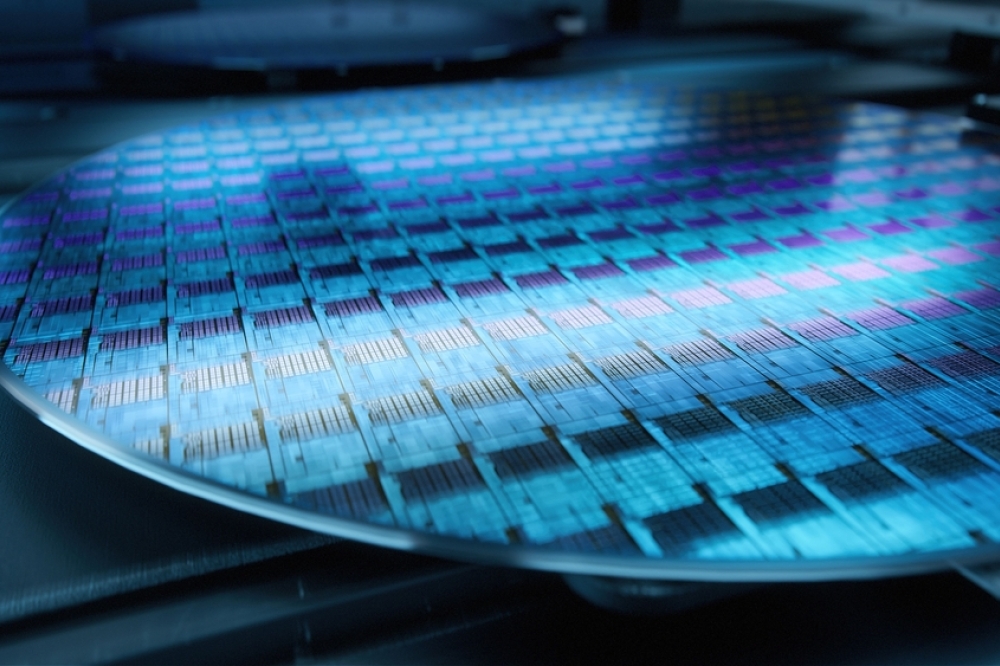

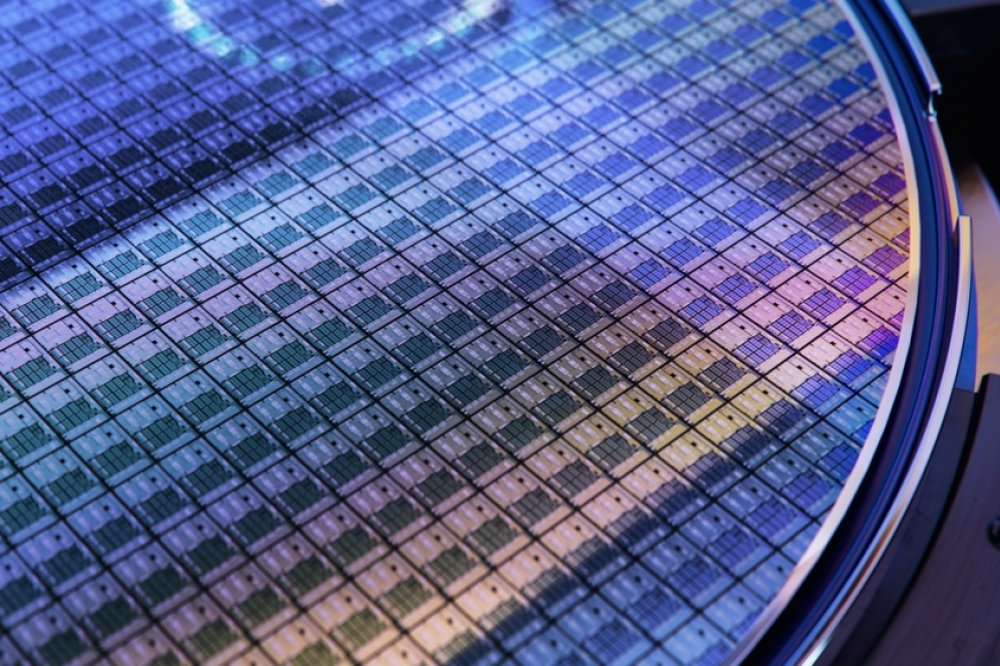

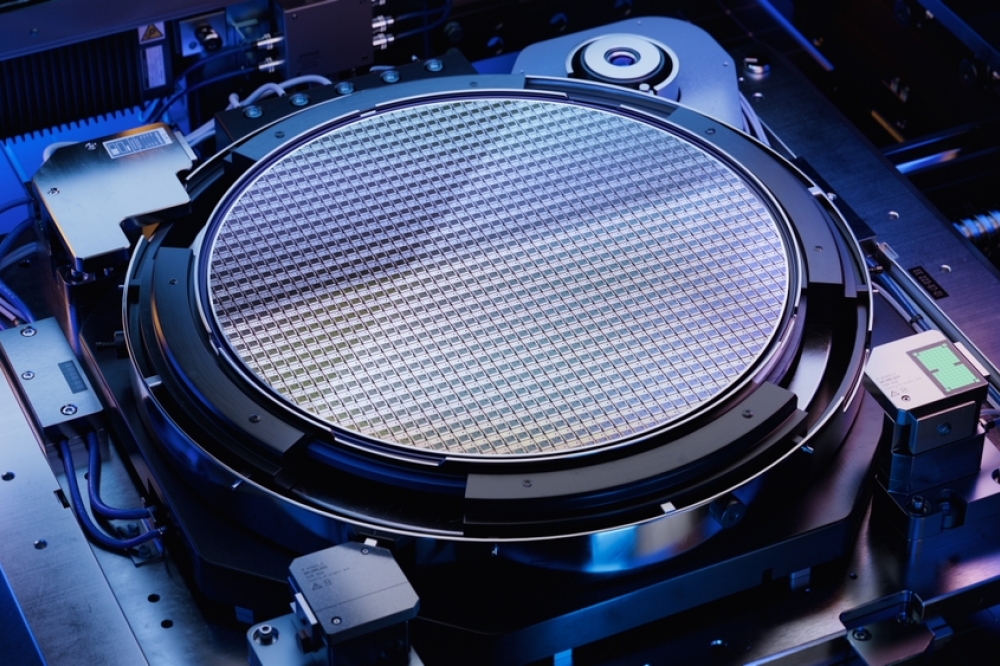

In the future, they will offer the complete value chain in 300 mm microelectronics and thus the prerequisite for high-tech research in future technologies with international reach. The 300 mm wafer industry standard is crucial in this context, because on the one hand it is the only way to ensure a rapid transfer of research results to the semiconductor industry in Saxony, nationwide and also worldwide. On the other hand, this wafer standard is a basic requirement to be able to successfully participate in new technology developments in the near-frontend sub-100 nm range. The center offers customers the opportunity to develop and test new manufacturing processes, as the stringent workflows in high-volume fabs such as Infineon, Globalfoundries or Bosch offer little scope for such test phases.

Among the persons (flnr): Prof. Harald Schenk (Director of the Fraunhofer IPMS), Sebastian Gemkow (Saxon State Minister for Science), Dr. Manuela Junghähnel (Site Manager of the new Center), Prof. Reimund Neugebauer (President of the Fraunhofer-Gesellschaft), Prof. Hubert Lakner (Institute Director of the Fraunhofer IPMS), Dr. Wenke Weinreich (Site Manager of the new Center), Dr. Manfred Horstmann (Vice President of the Fraunhofer-Gesellschaft). Hubert Lakner (Director of the Fraunhofer IPMS), Dr. Wenke Weinreich (Site Manager of the new Center), Dr. Manfred Horstmann (Vice President Globalfoundries Dresden), Prof. Martin Schneider-Ramelow (Director of the Fraunhofer IZM), Dirk Hilbert (Mayor of Dresden)

Introduction

With the Center Nanoelectronic Technologies CNT division of the Fraunhofer IPMS and the ASSID branch of the Fraunhofer Institute for Reliability and Microintegration IZM, two research facilities in the field of microelectronics that are unique in Germany are located in Saxony. Today, they are the only two German research centers for applied microelectronics research based on 300 mm wafer industry standard equipment. The core of the concept for the foundation of a joint center was to combine the scientific and technical competences of IZM-ASSID and IPMS-CNT with regard to research and development (R&D) in 300 mm front-end and back-end processes. On the one hand, this will increase efficiency and complete the value chain, while at the same time opening up new fields of research.

Semiconductor material screening and evaluation services

An important prerequisite for cooperations with industrial partners is the industry-compatible clean room of the new center, which houses an R&D technology platform with a plant procurement value of more than 120 million euros on an area of approx. 3,000m?. Crucially, in addition to the process equipment, the associated logistics (such as stockers and sorters) and all the measurement and analytical equipment are based on the 300mm industry standard. The IPMS-CNT conducts applied research in the front end of CMOS manufacturing. Fraunhofer IZM-ASSID complements this expertise with innovative packaging and heterointegration technologies.

The new center provides semiconductor manufacturers and suppliers with screening and evaluation services for materials, processes, chemicals and consumables from laboratory to production scale. Services include consumable benchmarking, process development, ultra large scale integration (ULSI), pilot production and equipment evaluation. Independent evaluation and test control with ISO 9001 certification is performed in a production-like environment with standard industrial equipment. This includes direct exchange of wafers with production lines (short loops) and professional contamination management. Pre- and post-processing of individual process steps are optimized to enable rapid scaling from laboratory scale to operational capability in a high volume fab.

The center can draw on more than 10 years of experience in introducing new materials into production and thus offers customers savings in resources, equipment investments, personnel and time (time-to-market).

Figure 2: View into the clean room of the new center on the 300 mm industry standard equipment. ©Fraunhofer IPMS

Insight into semiconductor research and manufacturing

Individual process development

An important core task of the center is the development, optimization and transfer of process and integration concepts with industrial partners. One example of this is the development of novel memory technologies for, among others, the long-standing industry partner Globalfoundries. The research on innovative processes carried out by Fraunhofer IPMS in the clean room and laboratories forms the basis for new reliable memory concepts as applied in embedded memory blocks as well as future neuromorphic computing concepts.

The ferroelectric hafnium oxide researched at Fraunhofer IPMS offers much potential for use in future chip generations for a wide range of applications. Due to the appreciable polarization property of the ferroelectric crystal structures, this material can be used for non-volatile data storage. Such concepts have been in use for many years. However, conventional ferroelectric memories are often based on lead-containing materials, such as PZT, which on the one hand require special precautions for processing in the clean room and on the other hand are less scalable.

Figure 3: Schematic of an FeFET memory transistor of the IPMS technology platform. ©Fraunhofer IPMS

In contrast, hafnium oxide is an established gate dielectric in newer transistor generations, which can be provided with ferroelectric properties by selective doping with e.g. silicon. Embedding this ferroelectric material in field-effect transistors results in FeFET memory transistors (Fig. 3), which can be scaled very well due to the very thin ferroelectric layer and can also be switched with low voltages. By applying electric fields, the polarization of the ferroelectric dipoles can be switched. With the field effect of these dipoles, the operating point of the FeFETs can be shifted and thus the stored information can be read out non-destructively (Fig.4a). In addition to the very high switching speed and low energy consumption, another major advantage is the ease of integration into existing semiconductor technologies.

As part of a research project, new approaches for the ferroelectric material stack in FeFET transistors were explored by process trials at Fraunhofer IPMS for the industrial partner Globalfoundries. Using a FeFET technology platform established in the clean room and wafer exchange with Globalfoundries, innovative process variants for optimizing the reliability and switching behavior of ferroelectric transistors were developed and tested. For example, a silicon nitride-based interface significantly increased the data retention of the memory cells (Fig. 4b). This process optimization was established at Globalfoundries and successfully demonstrated on scaled memory cells in the megabit range.

Screening and evaluation services

In addition to individual process development and process optimization, the CNT of Fraunhofer IPMS also offers screening and evaluation services for materials, processes, chemicals and consumables that are required and used in semiconductor fabs. For example, a long-standing cooperation agreement has existed between the CNT and BASF SE since 2014, which intends to jointly develop innovative solutions for the semiconductor industry. In this context, new chemicals for semiconductor processes such as plating and bonding are tested for BASF and process optimizations are carried out. In this context, BASF has installed a corresponding process plant of a renowned manufacturer at the CNT. This modern plating process plant for the electrodeposition of copper layers on 300 mm wafer scale is operated by the researchers of the Fraunhofer Center.

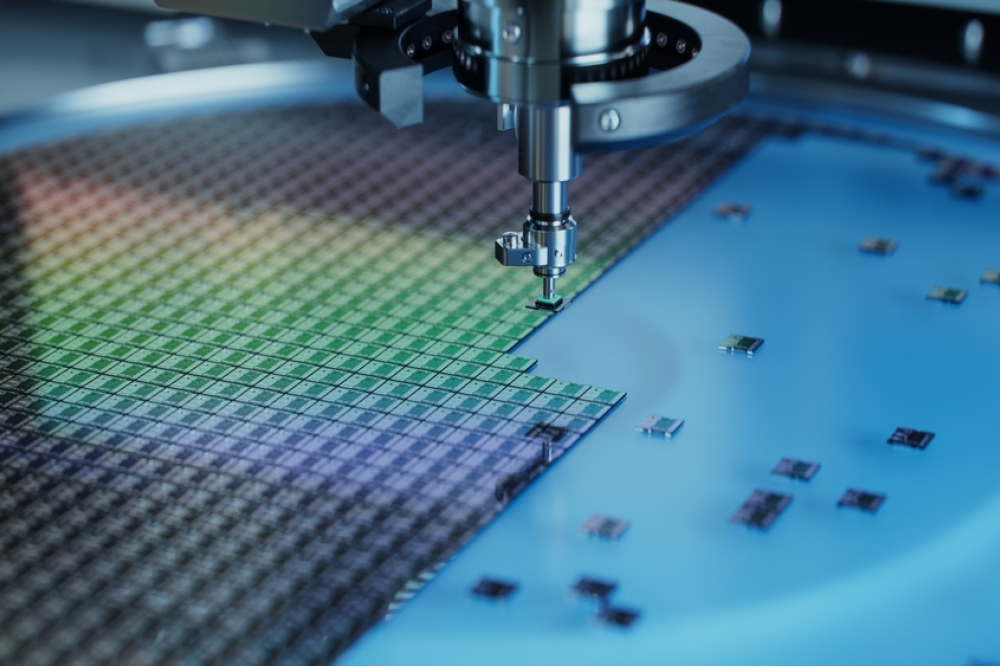

The technologies used in the screening include dual damascene plating processes for very small technology nodes down to less than 20 nm, as well as packaging technologies for chip wiring, in which trace materials are produced using RDL, TSV, pillar and bump plating for wafer level packaging applications.

Figure 4a: Current-voltage characteristics of an FeFET memory transistor for the two memory states programmed (red) and erased (blue) (Publication T. Ali et al. TED, 2018). ©Fraunhofer IPMS

The Fraunhofer Center’s work under the cooperation agreement includes research and development. In the area of electroplating, newly developed products from BASF are tested and ramp-ups to industrial scale are carried out. This includes the screening of chemicals, electrolytes and bath additives to deposit high-purity metal layers that will later be used in wiring structures in chip production. The Fraunhofer Center uses the system to test whether, for example, the deposition with new electrolytes currently under development is low-particle and produces a homogeneous layer on the wafer. The focus is also on investigating the properties of the deposited layers, such as grain size and orientation.

The second work area comprises demonstration and test trials. The facility is used to test BASF’s latest technologies and innovative chemicals on test wafers or short-loop wafers and to generate process data tailored to customers’ needs. In addition, parameter optimizations are carried out on production processes in order to further develop them and adapt them to new chip designs. The target parameter values to be achieved in the tests for metallization for wiring structures include good structure filling without voids and homogeneous structure and wafer surfaces. Since Fraunhofer is using the same equipment technology as is used by BASF’s customers, this enables significant cost and time savings for the chemical manufacturer. With the completion of the pilot tests at the Fraunhofer Center, customers can thus immediately use the ready-to-use processes for the production of advanced electronic materials. The further development of materials and processes makes it possible to meet the constantly increasing demands on microchips in terms of functionality, speed and energy efficiency.

Figure 4b: Comparison of data storage for two interface variants. With the nitride interface, a significant improvement in data retention was achieved in experiments. (Publication T. Ali et al. TED, 2018). ©Fraunhofer IPMS

Wafer characterization in the clean room and laboratory area

The physical and electrical characterization of wafers in the clean room and in the specialized analysis laboratories plays an important role. In order to be able to evaluate the processes and components of nanotechnology research with regard to their application properties and reliability, a broad portfolio of highly sensitive electrical and physical measurement technology exists at the Fraunhofer Center in Dresden.

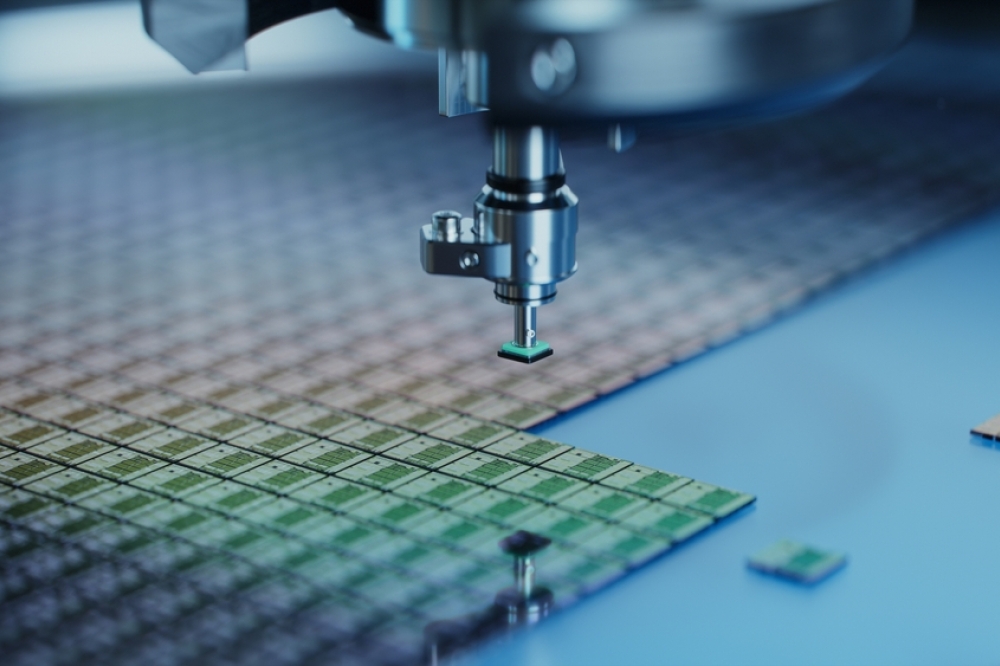

So-called inline measurements during the processing of wafers in the clean room can already provide initial insights into the functionality and electrical parameters of the manufactured structures in a non-destructive manner. This enables fast reaction times with regard to process adjustments and insights into the individual intermediate steps. After completion and ejection of the wafers, they can be analyzed with more in-depth analysis methods using highly specialized electrical and physical measurement technology.

The wafers produced are then loaded into wafer probers in the electrical test laboratory, either as a whole or as a single sample, and the components on them are electrically contacted by means of micrometer-fine probe needles. Using the connected measurement technology, it is then possible, for example, to characterize characteristic fields of integrated transistors, the frequency behavior of capacitors and high-frequency structures, the switching behavior of memory cells, or leakage currents of dielectrics up into the femtoampere range, to name just a few.

An important role is also played by the high degree of automation of the measurement procedures, which makes it possible to determine the electrical properties over entire wafers by means of statistical measurements in order to be able to draw conclusions about the uniformity of the wafer processes in the clean room.

Figure 5: Process control of development wafers at the Fraunhofer Center for Advanced CMOS & Heterointegration Saxony. ©Fraunhofer IPMS

This consistent automation of the electrical measurement technology, combined with the wide temperature range of the wafer probers from -55°C to 300°C, also enables complex, lengthy measurements at various test temperatures without manual intervention and thus scientific research into physical processes in materials as well as the consideration of reliability in real application scenarios such as those found in industry and automotive engineering. As already mentioned, an important focus in the electrical test lab at the Fraunhofer Center is the characterization of non-volatile data storage devices. Here, individual memory elements or even complex memory blocks can be statistically examined on a gigabit scale with regard to performance, data retention and other reliability parameters.

Extensive tests and measurements are being carried out for the mixed-signal foundry X-FAB to improve its chips. In this context, memories of the nvSRAM technology are analyzed in a joint research project. An nvSRAM combines the advantages of a very fast but volatile SRAM memory with the properties of a non-volatile memory by integrating corresponding memory cells into the SRAM circuits. Thus, in the event of a power failure in the system, the contents of the SRAM can be backed up within a few milliseconds, thus preventing data loss. At the Fraunhofer Center, larger nvSRAM memory blocks from X-FAB are being tested using fast mixed-signal test systems (24 analog and 96 digital channels) with regard to their switching characteristics, error rate and reliability under automotive conditions. The measurement results can be used to optimize memory technology and circuit design.

Figure 5: Process control of development wafers at the Fraunhofer Center for Advanced CMOS & Heterointegration Saxony. ©Fraunhofer IPMS

Cooperations of the Center

The implementation of joint research projects and cooperations with industrial companies is a core task of Fraunhofer. For example, the CNT division of Fraunhofer IPMS has already implemented projects with more than 100 customers. About a quarter of the industrial revenues come from Saxony, half from Germany (excluding Saxony). The largest customers include Globalfoundries, Infineon, BASF, X-FAB and Sony. In addition to orders from the major Saxon semiconductor manufacturers, there are numerous cooperations with smaller Saxon companies which, for example, do not have access to semiconductor foundries due to low volumes or specific material requirements. The CNT is also an important partner for the semiconductor supplier industry. For example, a novel environmentally friendly wafer cleaning technology developed by a Leipzig-based startup (Intelligent Fluids) was tested for the first time under industrial conditions at the CNT. Based on the project results, the technology is now being used directly by semiconductor manufacturers worldwide. The long-standing cooperation with BASF to test and further develop chemicals for chip production is another example of successful collaboration.

Further cooperations exist with Saxon universities, especially the TU Dresden, as well as with non-university research (e.g. HZDR, IFW). An example of this is the cooperation with the Max Plack Institute for Structural Physics in Halle, where a new promising research cooperation in the field of magnetic storage is currently being realized.

Figure 6: Electrical measurement technology at the Fraunhofer Center (left: automatic wafer prober, middle: semi-automatic wafer prober, right: semiconductor parameter analyzer). ©Fraunhofer IPMS

At the European level, there is close networking between the Fraunhofer Group for Microelectronics, the CEA-LETI in Grenoble (France) and the IMEC in Leuven (Belgium). The three leading European Research & Technology Organizations (RTOs) in the field of microelectronics are increasingly coordinating their R&D activities. For the current European Research Framework Program (HorizonEurope), for example, joint research priorities were coordinated according to the “Smart Specialization” approach and implemented, for example, through a joint application to create a European “Testing and Experimentation Facility (TEF) for Edge AI”.

The CNT, together with the IZM-ASSID, plays a key role for Germany in this European cooperation in the field of industry-related 300mm research. Without these two research sites, Germany would not be able to play an adequate partner role in this field in the European semiconductor research triangle Grenoble - Leuven - Dresden. Internationally, Fraunhofer IZM-ASSID is also closely intertwined with working groups in the field of wafer level integration, including Heterogeneous Integration Roadmap - HTA, CPMT- IEEE, Sematech.

Figure 7: Test structure contacted with test needles. ©Fraunhofer IPMS

Conclusion and outlook

The chips of the future should be three-dimensional, energy- and chemical-saving, environmentally friendly and inexpensive. The even more closely interlinked joint work of the Fraunhofer colleagues in the new Center for Advanced CMOS & Heterointegration Saxony will provide the best conditions for important impulses and research results to come from Saxony in future technologies.

For example, the Center’s scientists are working together in the field of quantum computing to ensure that quantum production will be CMOS-compatible and thus more scalable in the future.

The Center represents an important link and bridging function between basic research and industrial application. In the area of neuromorphic computing, researchers are working on new memory devices and accelerators on in-memory computing solutions for particularly energy-efficient AI solutions (Edge AI).

Figure 8: Statistical measurement with checkerboard wafer map and wafer signature

Services

In addition to direct contract research for companies and R&D collaboration in publicly funded projects, the Center offers numerous services, such as:

○ Nanopatterning by e-beam lithography for various substrates (e.g. Si glass) and sizes Processing of wafers (up to 300mm) with customer-specific layer structure

○ Test Wafer Evaluation

○ Studies on individual process steps such as CMP, ALD, DRIE, Cu Plating

○ Wafer cleaning

○ Screening and optimization of new chemicals and processes up to the 2x nm node

○ Qualification of equipment and components for high-volume semiconductor manufacturing under standard industrial conditions