Building trust in GenAI for semiconductor design with IP lifecycle management

While Generative AI (GenAI) technologies are already transforming software development and have great potential to improve semiconductor design, their adoption in this industry remains hindered by the challenges around protecting highly sensitive intellectual property (IP), the vast costs associated with errors, and the critical need to manage data provenance and liability.

By Vishal Moondhra, VP of Solutions Engineering, Perforce

The potential benefits of GenAI to accelerate and drive new efficiencies in semiconductor design means that there is a growing demand for these barriers and challenges to be overcome.

There is a critical need to create a solid strategy that protects IP while still enabling teams to use AI. One pillar that is being examined is to include IP lifecycle management (IPLM) processes — already part of many semiconductor design teams’ ways of working — to ensure better control and traceability around how data is used to train GenAI models.

Benefits and risks of GenAI in semiconductors

To understand how that can work in practice, it helps to have some more context around the benefits and risks.

When applied appropriately, GenAI can contribute to accelerated design cycles, improved design quality, enhanced validation and verification, simplified IP reuse, and increased capacity for experimentation and innovation, as well as collaboration and knowledge sharing. GenAI can provide teams with a significant head start, helping them overcome the limitations of human time and experience. For instance, currently, understanding and debugging errors is a time- and labour-intensive process.

With effective use of AI, engineers could receive guidance about the source or reason for the error, as well as suggestions around how others have tackled similar issues. Another example could be having an AI agent look for the best IP or design block to satisfy a particular aspect of a design project, again saving the design team time and effort. However, the advantages must be carefully balanced against the challenges and risks:

• Liability – pertaining to IP ownership and licensing of data used for training. If GenAI models are trained on proprietary or third-party data without proper controls, sensitive IP could be leaked via the outputs generated by AI. Given the massive investments that IP vendors have made in creating and selling their designs, control over their use – including preventing third parties from using that data to train AI models or having it used in unauthorised locations — is of

paramount importance.

• Lack of traceability, data quality concerns – it can be complicated to trace exactly how an AI model was trained. Yet traceability is essential to ensuring that the model is reproducible and that all data used in training is fully vetted for IP quality and maturity. If organizations don’t fully understand exactly what data and IP versions have been used to train the model, debugging becomes nearly impossible.

• High stakes – the cost and potential time delays resulting from errors can be ruinous. In the domain of software applications, errors and problems, while challenging, have reasonable recovery mechanisms. However, in the semiconductor domain, the situation becomes much harder. The later an issue is detected, the more expensive it is to fix. Mistakes that reach tapeout can run into millions of dollars to address. This massive financial risk is one of the primary reasons the semiconductor industry has been slow to adopt generative AI techniques. A badly trained model, with unknown provenance of the training data set, can easily lead to generating designs that are unviable, hard to verify or otherwise error prone.

Therefore, having complete control over the process to know what and how data is being used for training, including its full provenance, has to be the foundation of any semiconductor design project involving GenAI. Semiconductor leaders who are tasked with incorporating GenAI into the design workflow must establish firm guardrails for the data used to train internal models in order to achieve the level of trust required to open the door to AI adoption, move forward, and reap the benefits of AI. Trust is the bedrock of AI adoption.

To establish trust in using AI to train internal models, it is critical to have the following:

• Clear and auditable data provenance for all training datasets

• Complete traceability of all IPs and IP versions

• Secure and compliant use of both internal and external IP.

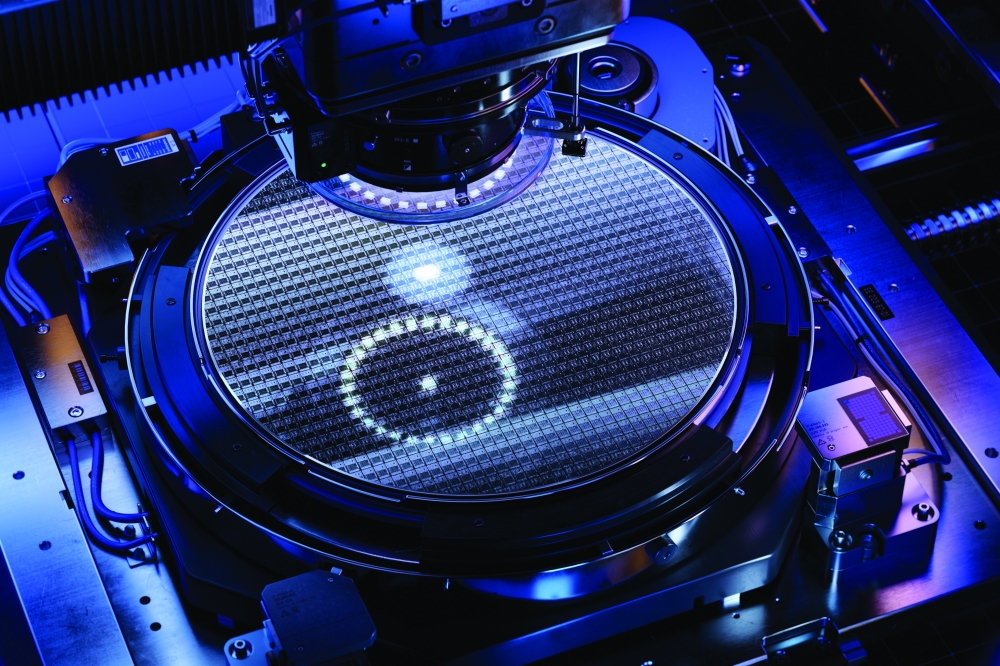

Breaking designs into blocks

So, how do we ensure that teams do not use the wrong data — or use it incorrectly – to train their AI models? The starting point is to segment designs into a set of individual, manageable IPs or blocks. IP lifecycle management (IPLM) techniques and tools can then be utilized to manage the lifecycle of the individual IPs.

By breaking a design into individual IPs, organisations can train AI models with specific, known, vetted and trusted blocks, as opposed to an opaque, monolithic design that may contain unauthorized, poor quality, or otherwise inappropriate IP.

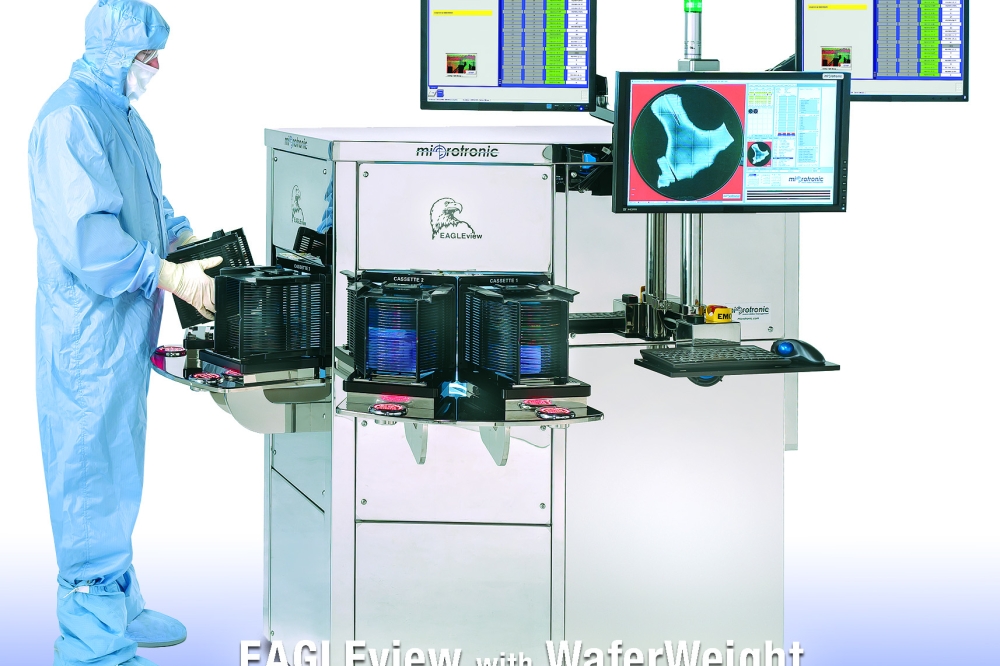

Increasingly deployed within the semiconductor business, IPLM follows data IP from acquisition or development through to qualification, distribution, and integration into design. IPLM makes it easier to see where each specific IP version has been used across all projects, as well as any outstanding bugs, derivative designs, and the status of verification. Fine-grained permissions can ensure that only IPs that has been authorised for use in AI models are available to include in model training, while geofencing protects IP from being used in an unauthorised country, even if user permission has been granted.

This end-to-end visibility, traceability, and IP security provides the control and transparency required to establish a trusted foundation for AI use in semiconductor design.

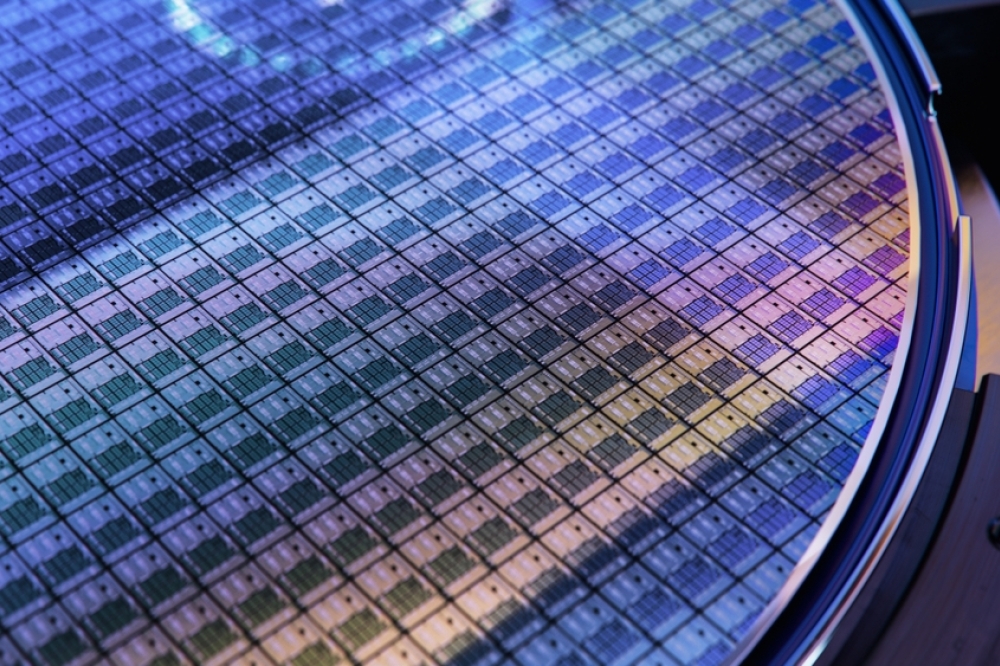

Ensuring data provenance and quality

With this comprehensive control and traceability, IPLM can also provide data provenance for AI training datasets. Data provenance is critical to ensuring full auditability of all designs. With IPLM, provenance can be established down to the IP version level, as well as for all associated metadata and even the design environment, ensuring that every possible variable contributing to the AI model is known, tracked, and auditable. Data can be modelled as a series of parent-child relationships to understand IP lineage, including the project(s) from which data was derived or copied.

Rules can be applied and enforced regarding the types of IP that can be used, as well as their source, to guard against contamination of the dataset and keep unauthorised IP from being incorporated into the training data. Rules can also be established to ensure certain standards for IP quality and maturity, as defined by organisations, are met before any data is used for AI training.

Consequently, semiconductor organisations can effectively build trust into their GenAI model training process, with the confidence to experiment and innovate more efficiently and safely. Furthermore, incremental training becomes possible, allowing users to see exactly what has changed since the last training set.

Training an AI model is a continuous process, not a one-time step. Users need to know: what happened in the past? How was that point reached? What is new, and what can be repeated?

These are all ways in which semiconductor teams can minimise the risks around AI use in semiconductor design while reaping the benefits. While the semiconductor industry has been cautious compared to others in its adoption to date of AI for design, the highly competitive nature of the semiconductor industry will soon force companies to move forward with AI to avoid falling behind, and organisations must be prepared.

Using IPLM helps establish and manage clear guardrails for safe, secure use of AI for semiconductor design teams. With AI’s widespread adoption inevitable, now is the time to create the right foundations to safeguard IP, mitigate business risks, stay competitive, and be ready for AI’s continued evolution.