Open-Silicon Breaks Barriers With First Hybrid Memory Cube Controller IP

Open-Silicon is introducing what it says is the industry's first Hybrid Memory Cube (HMC) controller IP core.

This high performance and flexible solution integrates

the many benefits of HMC technology into next-generation systems.

Targeting high-performance computing, networking and test & measurement applications, the HMC controller IP core offers high-bandwidth serial protocols derived from Open-Silicon's Interlaken controller IP core.

The company says HMC technology provides over 15 times the performance of a DDR3 module whilst using 70% less energy per bit than DDR3 DRAMs. Open-Silicon also says it takes up 90% less space than today's RDIMMs.

HMC technology is an entirely new category of high-performance memory, delivering low power in a dramatically reduced footprint. To benefit from this technology, next generation system developers need a high quality, customisable, and easy to integrate HMC controller IP to quickly get their products to market.

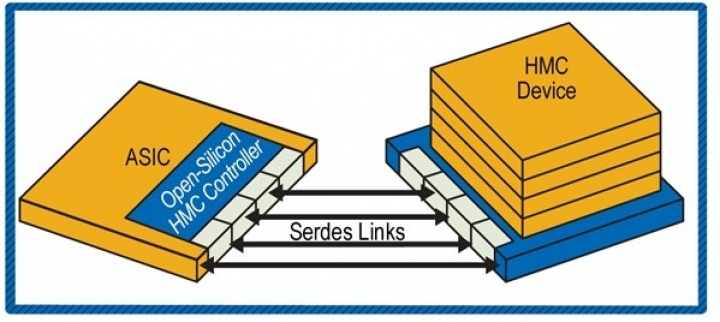

Open-Silicon's experience in complex ASIC development, combined with deep serial protocol IP expertise from developing six generations of Interlaken controllers, makes it a natural fit to offer this solution. As such, Open-Silicon joined the Hybrid Memory Cube Consortium (HMCC) as a developer member and has been using that collective experience to help craft the advanced specification requirements for the HMC interface.

"The mission of the Hybrid Memory Cube Consortium is to facilitate HMC integration into a wide variety of systems, platforms and applications," said Scott Graham, general manager of Hybrid Memory Cube for Micron Technology, co-founder of the HMCC. "We are excited by Open-Silicon's efforts to enable the adoption of HMC technology."

The IP offers a seamless way to interface with HMC. Supporting up to 240GBps, the high-performance HMC controller IP also offers ultra-low latency and a flexible user interface. As a fully synchronous, soft-core implementation suitable for ASICs and FPGAs, along with robust error detection and automatic retry, the core supports up to four HMC links managed by a single controller. Each link consists of 16 lanes of 10, 12.5 or 15 Gbps.