News Article

SPTS Doubles Silicon Etch Rates In TSV Processing

SPTS Technologies, a supplier of advanced wafer processing solutions for the global semiconductor industry and related markets, has announced its dry etch process technology for via reveal applications.

Already established at some major customer sites, SPTS says its Pegasus Rapier module offers a silicon etch rate at least twice as good as its nearest competitor, class-leading uniformities of +/- 2.5% on 300mm bonded TSV wafers, and the industry's only via reveal endpoint system, ReVia.

The Pegasus Rapier module etches silicon using Bosch switched processing as well as non-switched etching for tapered profiles, wafer thinning and via reveal.

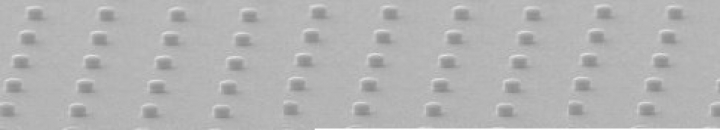

Via reveal, or post-TSV processing occurs after the through silicon vias (TSVs) are formed. The wafer is then temporarily bonded, face down, onto a carrier and ground typically to within 5 to 10 µm of the buried TSV's. The ground silicon surface is then dry etched, selectively to the TSV liner oxide, revealing the copper filled vias to a height of around 5 µm. After silicon etching, these via tips are passivated with further dielectric and then polished by chemical mechanical planarisation (CMP) to expose the copper ready for RDL (redistribution layer) metallisation.

TSV wafer thickness, carrier wafer thickness, bond layer uniformity, TSV etch uniformity and back-grinding uniformity all contribute to a significant incoming total thickness variation (TTV), which can cause issues with subsequent process steps.

Addressing these issues, the SPTS Pegasus Rapier module allows flexible multiple mode operation with its dual source design. In its principal mode, optimum etch depth uniformity is achieved to an edge exclusion of 3mm, preserving the TTV of "˜good' incoming wafers. Also, if required, alternative operating modes are available where the silicon can be etched with centre-fast or edge-fast profiles to rectify "˜problematic' incoming TTV, delivering a more uniform outgoing wafer.

Due to grind rate uncertainties, it is essential that the point at which the vias are revealed can be detected in-situ.

Without endpoint, the user has to independently measure the silicon thickness above the TSVs on every wafer and adjust the etch time accordingly; adding cost, complexity and risk of yield loss in the process flow.

The ReVia end-point system detects the point at which the TSV tips are revealed, enabling a consistent reveal height from one wafer to the next, increasing yields and avoiding scrap. Via reveal processes on wafers with via densities of less than 0.01% have been successfully end-pointed.

"Etch rate, uniformity control and end-point detection all play their part in delivering the lowest cost per die and the highest yield at a point in the fabrication process where the wafers have an extremely high value," said Dr. Dave Thomas, Marketing Director for etch products. "Our innovative dual source reactor design coupled with our competence in developing and integrating novel end-point techniques, is maintaining our leadership in this area of the Advanced Packaging market."