MoSys Develops Integrated 384 Gbps Bandwidth Engine IC

The firm's second generation silicon architecture extends performance by up to two times and adds intelligent error management capabilities

Fabless semiconductor company MoSys based in Santa Clara has unveiled a second generation Bandwidth Engine device optimised for high-speed buffering applications.

The device has higher speed interfaces than the previous model and is designed and built for high-reliability, carrier-grade applications.

The MSR620 extends the Bandwidth Engine capabilities by incorporating cycle selectable burst functionality to support variable packet sizes with improved interface efficiency. The high access rates and effective throughput on the MSR620 buffer device are well suited to the requirements for 200GE and 400GE traffic management, packet classification, oversubscription buffering or egress buffering.

Using sixteen 15 Gigabits per second (Gbps) SerDes lanes, the MSR620 interface operates at 480 Gbps, providing the host with up to 384 Gbps CRC protected, effective data throughput. This represents an 80 percent overall efficiency, which MoSys says is well beyond the capability of standard memory subsystems and alternative serial interface solutions, while occupying less board area, using fewer interface pins, and consuming less power.

With finer process geometries and lower voltages, error susceptibility is inherent and a growing issue. The second generation bandwidth engine architecture keeps ahead of this curve by making advanced built-in self test and repair capabilities available to customers. This optional feature is another layer of protection enabling customers to deliver systems with enhanced uptime performance.

"The addition of the burst functionality and higher interface rates gives the MSR620 unparalleled performance in high data rate applications while reducing board area, power and system cost," says John Monson, Vice President of Marketing for MoSys. "Already leading the industry with Bandwidth Engine access rates, throughput and integrated intelligence, we are also excited to be at the forefront of the growing requirement for self-healing solutions. These capabilities will become more critical as geometries and voltages continue to shrink."

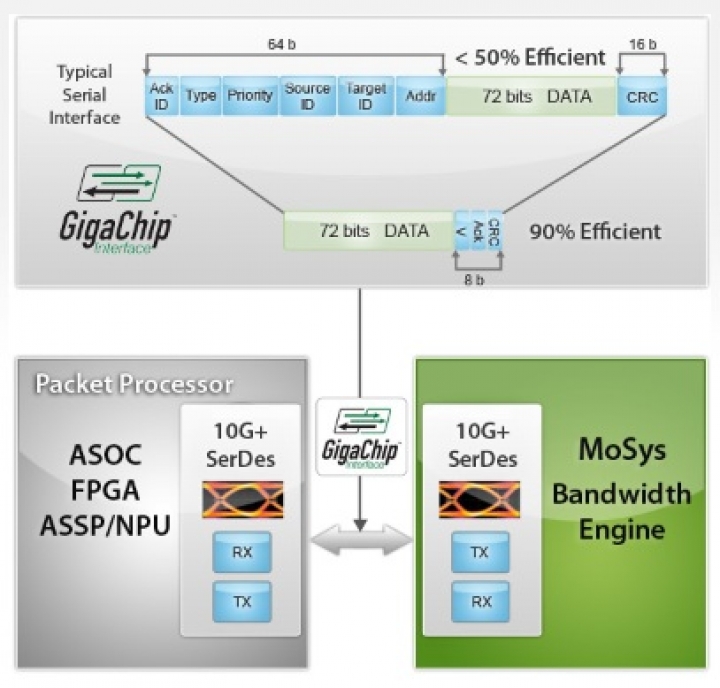

MoSys' Bandwidth Engine family of ICs utilise the GigaChip Interface, an open, 90 percent efficient, transport protocol optimised for chip-to-chip communications. The device is compatible with CEI-11G and XFI SerDes, which allows a seamless interface with high performance FPGAs as well as standard libraries available from ASIC providers. A complete package of RTL and tools is available to support the Bandwidth Engine interface.

The firm's Bandwidth Engine IC has been fully qualified for carrier-grade applications and is available for volume production now.