Yole: UMC Gets Set To Compete In The 2.5/3D Foundry Space

At the recent Semicon Taiwan conference, Kurt Huang, Director of Marketing at UMC gave a presentation entitled "Foundry TSV Enablement For 2.5D/3D Chip Stacking".

The presentation made it clear that UMC will be ready to compete with TSMC in the foundry interposer and 3D stacking business.

The firm sees several work flow models and points out that each OSAT / foundry will have its own capabilities and preferences. Also work flow optimisation may depend on BOM cost, stack recipe and test strategy.

![]()

Ecosystem work flow models

UMC indicates that its foundry design rules for interposer fabrication are ready to go with product level packaging & testing and reliability assessment scheduled for completion in 4Q 2012.

![]()

UMC ground rules and document status

The company says it will use mainstream, via-middle copper TSV technology. RDL on the interposer will use its 65nm BEOL technology and 3D will initiate with 28nm CMOS logic.After 28nm USMC says TSV for 3D may come as a standard option for foundry CMOS logic at 20nm and beyond.

Cross sections of UMC Si interposer and 3DIC stack

TSVs are formed after CMOS but before contact/metal as shown below

![]()

Insertion of TSV into the process flow

According to Yole, USMC's TSV formation process flow will follow the following sequence:

![]()

Process flow for TSV formation and fill

Typical 3D TSV are 6 x 50 and for interposer are 10 x 100 µm. KOZ have been determined to be 5µm for 28nm HKMG core device with TSV pitch: JESD229 50/40µm.

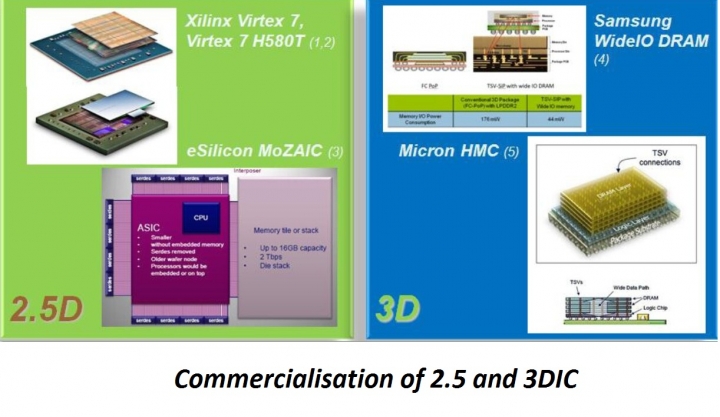

As specific product examples UMC showed 2.5D solutions by Xilinx and e-Silicon and the 3D wide IO memory stacks of Samsung and Micron.