Graphene Optimises Spin-Polarision Contacts On Silicon

Using graphene provides a very uniform, inert and solid tunnel barrier which is free of defects and states which plague oxide barriers

Researchers at the NRL have demonstrated that graphene can serve as a low resistance spin-polarised tunnel barrier contact.

And it successfully enables spin injection/detection in silicon from a ferromagnetic metal.

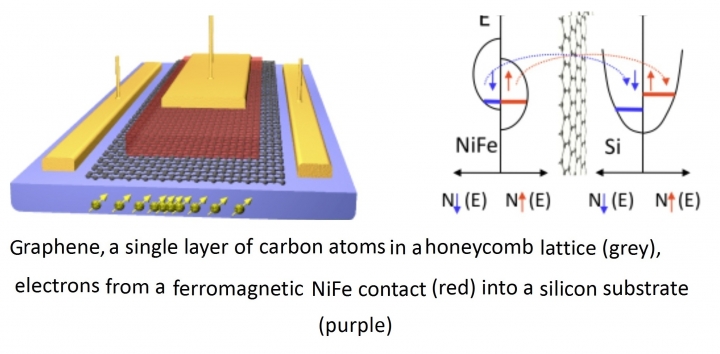

The scientists at the Naval Research Laboratory (NRL) used a single layer of carbon atoms in a honeycomb lattice. The graphene provides a highly uniform, chemically inert and thermally robust tunnel barrier free of defects and trap states which plague oxide barriers.

The researchers, led by Berend Jonker, say this discovery overcomes an important hurdle in the development of future semiconductor spintronic devices. These are devices which rely on manipulating the electron's spin rather than its charge for low-power, high-speed information processing beyond the traditional size scaling of Moore's Law.

The NRL research team includes scientists from the Materials Science and Technology Division and the Electronics Science and Technology Division. Back row: Adam Friedman, Berend Jonker, Olaf van 't Erve. Front row: Jeremy Robinson, Connie Li, Enrique Cobas

Ferromagnetic metals, such as iron or permalloy, have intrinsically spin-polarised electron populations (more "spin-up" electrons than "spin-down", as seen in the figure at the top). They are thus ideal contacts for injection and detection of spin in a semiconductor.

The net spin accumulation in the silicon produces a voltage, which can be directly measured. Spin injection, manipulation and detection are the fundamental elements allowing information processing with the electron spin rather than its charge.

An intervening tunnel barrier is required to avoid saturation of both semiconductor spin channels by the much larger metal conductivity. This would otherwise result in no net spin polarisation in the semiconductor.

However, the oxide barriers typically used, such as Al2O3 or MgO, introduce defects, trapped charge and interdiffusion, and have resistances, which are too high. All of these factors severely hinder the device performance.

The team's novel approach of using a single layer of graphene as the tunnel barrier utilises a defect resistant, chemically inert and stable material with well-controlled thickness. It achieves a low resistance spin contact compatible with both the ferromagnetic metal and the semiconductor of choice. These qualities insure minimal diffusion to and from the surrounding materials at temperatures required for device manufacturing.

The scientists demonstrated electrical generation and detected spin accumulation in silicon above room temperature. They showed that the contact resistance-area products are 100 to 1000 times lower than achieved with oxide tunnel barriers on silicon substrates with identical doping levels.

These results identify a new route to low resistance-area product spin-polarised contacts. This is a key requirement for semiconductor spintronic devices that rely upon two-terminal magnetoresistance, including spin-based transistors, logic and memory, explains NRL's Berend Jonker.

The NRL team suggests it will next use multilayer graphene in such structures. This may provide much higher values of the tunnel spin polarisation due to band structure derived spin filtering effects which have been predicted for selected ferromagnetic metal / multi-layer graphene structures.

This increase would improve the performance of semiconductor spintronic devices ; It would provide higher signal to noise ratios and corresponding operating speeds, advancing the techological applications of silicon spintronics.

The research results are reported in more detail in the paper, "Low-resistance spin injection into silicon using graphene tunnel barriers," by O. M. J. van 't Erve et al, in Nature Nanotechnology, published online on September 30th, 2012 (DOI 10.1038/nnano.2012.161).