Pivotal milestones in silicon photonics and the NanoIC pilot line

Imec has been as busy as ever, collaborating with Veeco Instruments to accelerate datacom and quantum computing applications, as well as sharing recent NanoIC pilot line developments

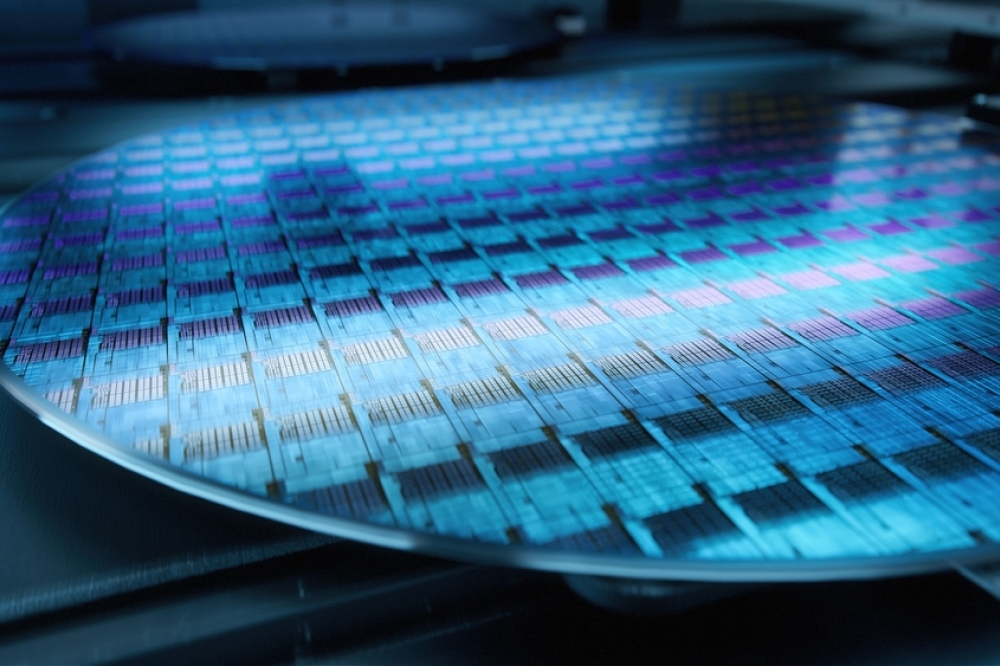

Veeco Instruments and imec announced have collaboratively developed a 300mm high volume manufacturing compatible process that enables the integration of barium titanate (BaTiO3 or BTO) on a silicon photonics platform. BTO is a promising material with unique electro-optical properties that can be used for high-speed and low-power light modulation in emerging applications such as high-speed optical transceivers, quantum computing, light detection and ranging (LiDAR), and AR/VR applications. Historically, approaches to integrate BTO have struggled to meet the desired cost targets to make it viable for high-volume manufacturing.

Veeco has now delivered its first Molecular Beam Epitaxy (MBE) based cluster system, marking a significant milestone in Veeco’s and imec’s partnership and their dedication to enhance silicon photonics platform capabilities. The new 300mm platform is designed for the epitaxy of BaTiO3 single crystalline thin films on silicon, available with both solid and hybrid Molecular Beam Epitaxy (MBE) solutions. With the integration of these alternative growth techniques, the system will be capable of BTO-on-Si deposition with improved repeatability and at a lower cost than classical MBE methods.

The optical transceiver market for datacom is expected to grow to $13.1 billion in 2030, up from $2.9 billion in 2024. However, to alleviate the trade-offs of current silicon modulator technologies, including high power consumption, performance (speed, drive voltage), and area, the introduction of novel electro-optic materials, like BTO, into silicon photonics will be crucial. At present, there is no commercially available production-compatible solution for manufacturing these materials. In partnership with Veeco, imec is now addressing this industry need to develop scaled solutions that allows the integration of materials such as BaTiO3 and SrTiO3 onto a 300mm silicon platform.

“Over the past 4 years, imec and Veeco have collaborated on developing alternative techniques for BaTiO3-on-Si and benchmarking both material and electro-optic properties towards defining a strategy for advancing large-scale manufacturing solutions,” says Clement Merckling, Scientific Director at imec. “With the introduction of Veeco’s first-of-its-kind MBE solution, we are expanding our capabilities for heterogeneous integration of beyond-Si electrooptic materials, strengthening our R&D offering for current and new partners with an interest in exploring and prototyping next-generation silicon photonics technology.” added Joris Van Campenhout, imec Fellow and Optical I/O Program Director.

“This partnership with imec is a monumental step forward for the MBE industry, datacom and quantum computing production,” commented Matthew Marek, Senior Director of Marketing for Veeco’s MBE Product Line. “The historic view of MBE processing has been that it is slow and expensive; however, new hardware developments that our team validated in partnership with imec bring MBE into a cost-effective domain that is suitable for semiconductor fabs. We are excited about the work underway between our two organizations to demonstrate a repeatable, high-volume BTO production process. We anticipate this effort will help us achieve our shared goal to unlock BTO photonic modulator breakthroughs for a better and greener future.”

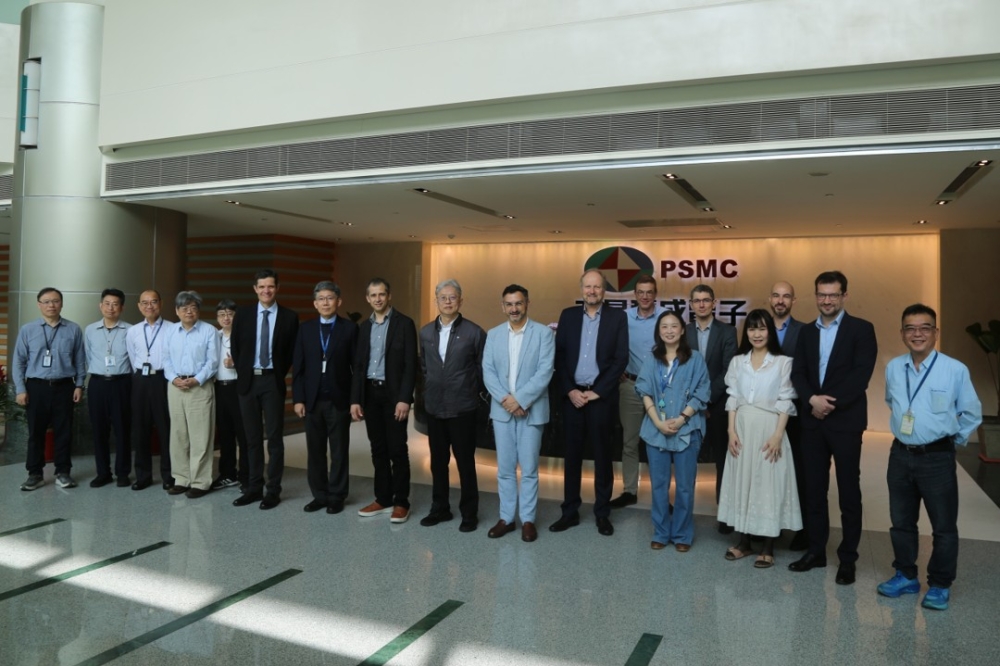

Imec inaugurates NanoIC pilot line

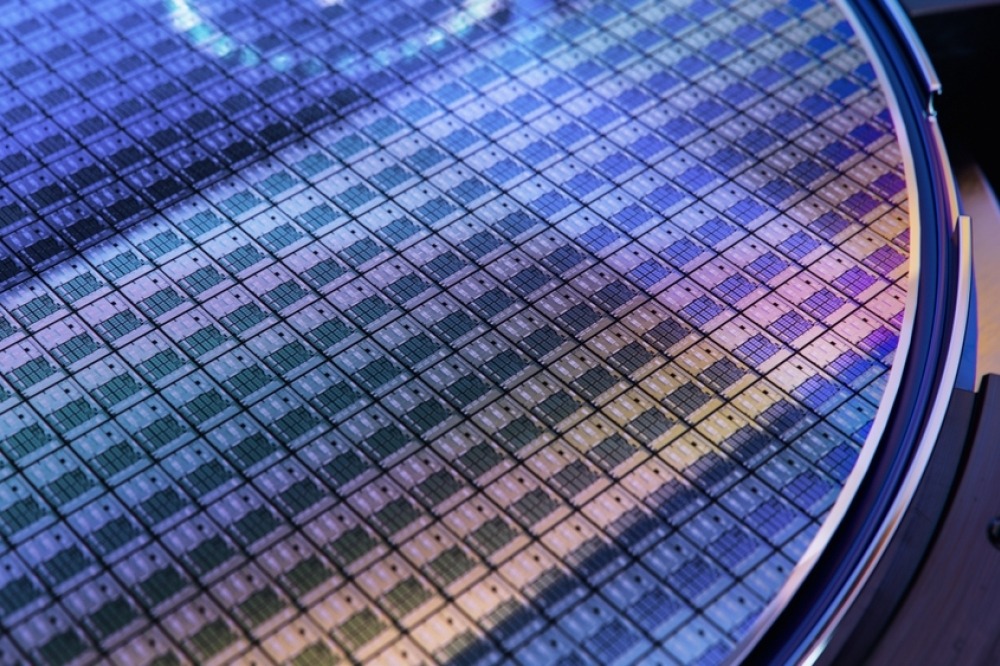

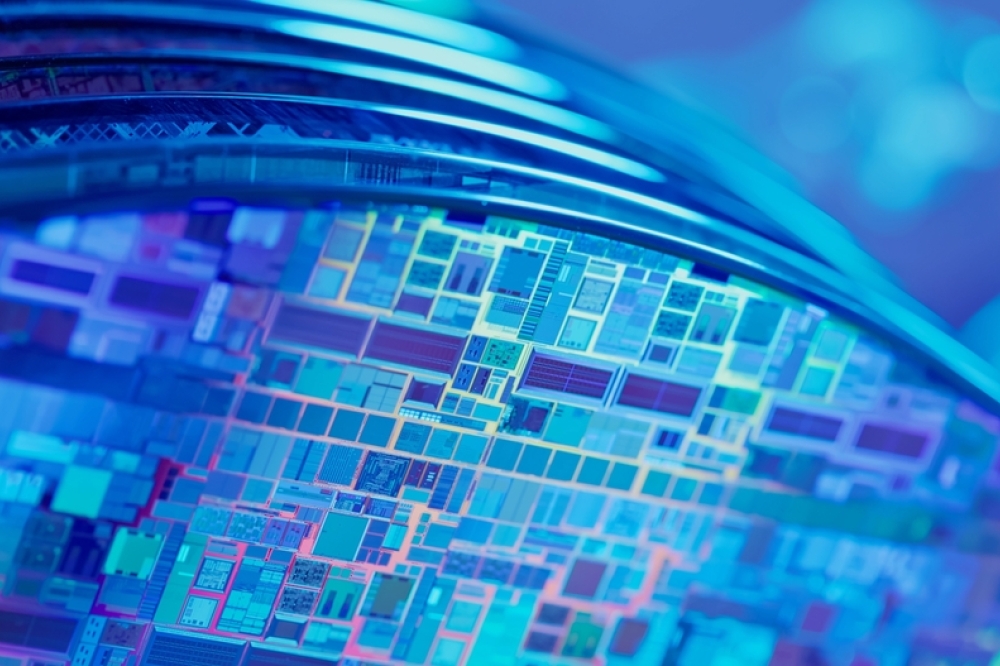

Imec recently inaugurated a 2,000m² cleanroom expansion at its Leuven headquarters, marking a pivotal milestone in the deployment of Europe’s NanoIC pilot line. The event was attended by European EVP Henna Virkkunen, Belgian Prime Minister Bart De Wever, Flemish Minister-President Matthias Diependaele, and ASML CEO Christophe Fouquet, alongside representatives from the European high-tech ecosystem – including industry and startups – the NanoIC pilot line consortium, and policymakers from the EU, Belgium, and Flanders. With a capacity of over 12,000 m², imec’s cleanroom plays a crucial role in the European Chips Act’s ambitions to position Europe at the forefront of next-generation semiconductor innovation and manufacturing; a strategy that will be instrumental in reinforcing the continent’s industrial fabric in the AI era, while safeguarding a climate of sustained economic growth, security, and prosperity for decades to come.

“Since announcing in May 2024 that imec would host the NanoIC pilot line, we’ve moved at full speed – accelerating tool acquisition and launching a comprehensive recruitment program. Today, that effort culminates in the inauguration of a 2,000m² cleanroom extension at the imec premises. It will house a best-in-class toolset, including ASML’s next-generation High NA EUV scanner that is scheduled to arrive mid-March,” said Luc Van den hove, CEO of imec.

“Imec researchers are working here side by side with IDMs, foundries, equipment and materials suppliers, system companies, start-ups, universities, and fellow European RTOs. Together, we have embarked on an ambitious journey to push semiconductor technologies beyond the 2nm node. By providing access to cutting-edge semiconductor technologies, the NanoIC pilot line will play a crucial role in strengthening Europe’s industrial fabric in the AI era, and ensuring a climate of economic growth, security, and prosperity for decades to come,” he added.

Imec’s cleanroom provides the foundation for NanoIC’s PDKs, based on 2 nm process flows.

Strategic importance and future outlook

And the momentum continues. With strong backing from the European, Belgian, and Flemish governments – and a robust network of industry partners – imec will soon begin construction of a whole new 4,000m² cleanroom at its Leuven campus, another key asset to bring Europe’s NanoIC initiative to full cruising speed. Over the next five years, the NanoIC pilot line will integrate more than a hundred new tools, distributed across imec and partner sites at CEA-Leti (France), Fraunhofer (Germany), VTT (Finland), CSSNT-UPB (Romania), and Tyndall National Institute (Ireland).

“We don’t have the luxury of being the biggest or the strongest, but we do have the choice to be the best,” explains Matthias Diependaele, Flemish Minister-President. “Imec brings together talent, knowledge, and international collaboration. With the NanoIC pilot line, Europe is making that choice a reality: for technological excellence and strategic independence. The fact that imec is hosting this pilot line underscores the exceptional strengths that Flanders has developed in research and innovation. Here, we are demonstrating how a world-class region can shape the chip technology of tomorrow.”

A step forward for European semiconductor leadership

Christophe Fouquet, President and CEO of ASML commented: “Today we are making a step forward in strengthening the chip technology ecosystem in Europe to serve our customers, the world’s chipmakers. Through our 40 years partnership at imec, together we have been driving faster innovation, fostering stronger collaboration, and supporting the development of regional talent, all of which are needed to support the advancement of the worldwide chip industry and AI. We are today inaugurating the NanoIC pilot line, that includes ASML’s High NA EUV system and which is the best example of what we can do when worldwide leaders in technology partner to bring together their latest technology and talent. Thanks to the strong support of EU President Von der Leyen and the European Chips Act, we are all very proud and thankful that this is happening at the heart of Europe and will allow Europe to play an even more critical role in the global semiconductor ecosystem”

NanoIC extends its PDK portfolio

The NanoIC pilot line, a European initiative coordinated by imec and dedicated to accelerating innovation in chip technologies beyond 2nm, has released two new process design kits (PDKs): an A14 pathfinding PDK for advanced logic scaling and an eDRAM system exploration PDK for advanced memory innovation. Both PDKs are firstoftheirkind releases, providing early access to cutting-edge design rules and flows, and giving users a unique gateway to investigate advanced technology nodes and embedded memory designs.

The advanced Process design kits (PDKs) from the NanoIC pilot line play a key role in advancing semiconductor innovation. They give designers early access to realistic design rules and implementation workflows long before hardware for a new technology exists. With the introduction of the A14 and eDRAM PDKs, NanoIC for the first time gives designers early insight into two critical technology areas for future compute systems: logic scaling at the A14 Angstrom node and embedded memory integration.

By making these PDKs freely accessible, NanoIC seeks to connect early-stage design exploration with real-world integration, helping researchers and startups explore emerging nodes, anticipate integration challenges, and benchmark designs against realistic scaling metrics. “PDKs like A14 and eDRAM are catalysts for learning and design”, Marie Garcia Bardon, Department Director at imec and work package leader within the NanoIC project, explains. “They offer a robust environment for hands-on evaluation and quantitative comparison of different technology choices. This approach accelerates learning, de-risks architectural and design innovation, and helps designers prepare for advanced logic nodes and embedded memory technologies well before hardware becomes available.”

“By making these PDKs broadly accessible, we lower barriers for universities, industry, and startups to engage with next-generation technologies”, Giuseppe Fiorentino, program manager for NanoIC continues. “Access to realistic rules and flows enables teams to explore new research directions and breakthrough concepts that will feed directly into the European semiconductor value chain.”

A14 pathfinding PDK: scaling down to the 14-Angstrom node

As the first of the newly launched PDKs, the A14 pathfinding PDK provides a virtual design environment for exploring scaling at the 14Angstrom node, one of the next major steps in device miniaturization. A key innovation at this node is the introduction of a direct backside contact as a new scaling booster. Whereas the earlier N2 PDK supported backside power delivery through TSVMiddle (TSVM) structures, the A14 node advances this concept by replacing TSVM with a more compact direct backside contact scheme. By routing power directly from the wafer’s backside to the gates and removing the need for complex topside metal routing, this architecture reduces IR drops and delivers an 18% area gain and 7% power reduction compared to N2 at iso frequency and cell density.

Imec is the first to release a PDK at this node. The kit includes a comprehensive 162SDC library and is supported by two major EDA vendors, Cadence and Synopsys.

eDRAM system exploration PDK: enabling embedded memory exploration

Complementing the logic pathfinding work enabled by the A14 PDK, the NanoIC pilot line also introduces a first eDRAM system exploration PDK, an important step toward addressing one of the biggest challenges in advanced systems: providing dense, low-latency on-chip memory. Central to this effort is bringing memory closer to the processing units, a key strategy for reducing latency and improving power efficiency in advanced compute architectures.

The current eDRAM PDK provides a virtual platform for exploring embedded memory solutions that bridge the gap between dense but power-hungry off-chip DRAM and fast but area-limited on-chip SRAM. With a focus on systemlevel behavior in dataintensive and AI workloads, it enables researchers to evaluate new memory architectures and integration strategies that bring higherdensity memory closer to processors and GPUs, reducing data movement, improving energy efficiency, and enhancing overall system performance.

Looking ahead, the eDRAM PDK will evolve into a full system exploration platform. This next phase will allow designers to move beyond virtual validation and analyze complete system-level interactions. As the platform matures, future development steps include hardware validation and, eventually, opportunities for tapeout and prototyping on the NanoIC pilot line.

Access and training opportunities

Both PDKs, together with the previously launched N2 PDK, are available through Europractice. To encourage adoption and hands-on exploration, NanoIC will also host a dedicated workshop on the N2 and A14 PDK on March 25–26, 2026, and on the eDRAM PDK on May 26, 2026. These workshops will offer practical guidance, technical insights, and direct interaction with the development teams. All practical details and registration are available on the NanoIC website.

This work has been enabled in part by the NanoIC pilot line. The acquisition and operation are jointly funded by the Chips Joint Undertaking, through the European Union’s Digital Europe (101183266) and Horizon Europe programs (101183277), as well as by the participating states Belgium (Flanders), France, Germany, Finland, Ireland and Romania. For more information, visit nanoic-project.eu.

NanoIC adds advanced SRAM memory macros

NanoIC pilot line has also released the N2 P-PDK v1.0, an important update of its N2 Pathfinding Process Design Kit (P-PDK). This new version introduces several new features, including a library of 29 SRAM memory macros, allowing designers to explore and benchmark system-on-chip (SoC) designs with frontside and backside power routing. By adding the SRAM macros in the design options, the N2 P-PDK v1.0 marks an important milestone in enabling research, learning, and design exploration on advanced and future nodes.

Towards next-generation SoC designs

As chip technologies scale beyond 2nm, the ability to explore full System-on-Chip (SoC) architectures with novel technology enablers becomes increasingly important. SoCs, integrating logic, memory, and interconnect capabilities into a single chip, are the backbone of a wide variety of digital applications, from smartphones and AI accelerators to automotive controllers. However, early-stage SoC design exploration is often constrained by limited access to complete and realistic design kits that include advanced or future technology scaling boosters such as power delivery networks. This gap makes it difficult for designers to validate architectural concepts, experiment with emerging technologies, or to train the next generation of chip designers on advanced nodes.

NanoIC’s low-barrier N2 P-PDK v1.0 aims to bridge this gap, offering instant access to a wide variety of new design features, including a portfolio of 29 ready-to-use SRAM macros with both frontside and backside power routing configurations.

This dual configuration, offered for the first time in a pathfinding PDK, enables designers to experiment with and optimize memory integration within realistic, advanced power networks. As a result, NanoIC’s N2 P-PDK v1.0 now provides the building blocks of a complete SoC as well as the architectural context to explore how those blocks interact within realistic power networks. It enables users to move beyond simple logic design and explore and validate full SoC systems that reflect the challenges and opportunities of next-generation semiconductor design.

Lowering barriers for learning and exploration

By making these advanced features freely available to academic researchers, startups, and design teams, NanoIC significantly lowers the barriers to innovation, empowering the development of next-generation applications, and strengthening Europe’s position in the global semiconductor landscape.

“This v1.0 version of our N2 P-PDK enables designers to evaluate the impact of new technology features and integration options on their designs before they exist in foundry offerings. It provides a unique environment to connect technology pathfinding with practical design enablement, ensuring that breakthroughs in device research translate into system-level advances.”, Marie Garcia Bardon, Department Director at imec and work package leader within the NanoIC pilot line, summarizes.

Building on the learnings from the previous N2 P-PDK, this release lays the groundwork for future PDK iterations, launching additional advanced logic, memory, and interconnect PDKs in the coming years. The roadmap includes future versions of the N2 P-PDK, as well as upcoming A14 and A7 logic P-PDKs, eDRAM and SOT memory PDKs, and advanced interconnect solutions (RDL, hybrid bonding, interposers), empowering innovation across the full spectrum of next-generation chip technologies.

Imec unveils 7bit, 175GS/s massively time-interleaved slope-ADC

At the recent IEEE ISSCC 2026, imec – a world-leading R&D center in advanced semiconductor technologies – unveiled a 7bit, 175GS/s analogtodigital converter (ADC) that combines a record-small footprint (250 x 250µm²) and low conversion energy with one of the fastest sampling speeds ever reported. As such, imec’s ADC meets the rapidly increasing throughput and processing demands of AI- and cloud-driven data centers, without the area and power explosion typically seen at ultra-high sampling rates.

Driven by AI and cloud applications, data centers’ optical communication networks need constant upgrades to handle ever-higher throughputs and processing demands. But as sampling rates climb beyond 100GS/s, the underlying components – such as wireline ADCs, essential in optical transceivers – tend to grow in size, requiring longer interconnects, and introducing parasitics and energy loss.

At the 2024 edition of the IEEE International Solid-State Circuits Conference (ISSCC), imec tackled this challenge with a breakthrough: a massively time-interleaved slope-ADC architecture at least twice as compact as conventional designs and featuring state-of-the-art power efficiency. Building on that approach, imec now takes the next step with the introduction of a record-small ADC that ensures precise signal conversion and wide bandwidth at ultra-high sampling rates.

Patented linearization and switched input buffers techniques

“Our 7-bit, 175GS/s ADC – implemented in 5nm FinFET technology – pairs a record-small core area of 250 x 250µm2, and low conversion energy (2.2 pJ per sample), with a sampling speed that ranks among the fastest ever reported. This makes it a compelling solution for upscaling digitalintensive wireline interconnects, where every square micron and milliwatt count,” said Peter Ossieur, portfolio director at imec. Two patented innovations make this possible. First, a novel linearization approach – shaping the slope signal – corrects distortions. Second, switched input buffers efficiently feed the ADC’s 2,048-channel time-interleaved array, minimizing electrical load and enabling ultra-fast sampling without compromising signal integrity.

Pushing toward – and beyond – the 300GS/s milestone

Building on the ADC presented at this year’s ISSCC, imec is now developing a 3nm followon design and exploring 14 Ångstrom designs, in particular how such advanced nodes can be leveraged for

high-performance wireline data converter designs.

Peter Ossieur comments: “Imec has a long-standing track record in developing high-speed integrated circuits for communication applications. One of our key research tracks focuses on optical transceivers (and their building blocks) that can keep pace with the rapidly increasing data rates in wireline systems. In this context, our ADCs represent a crucial step toward a new generation of compact, low-power converters for future wireline applications, pushing beyond the performance limits of SAR-based ADC architectures at ultra-high speeds. To accelerate this effort, we warmly invite partners – including fabless companies developing wireline connectivity building blocks – to join our ADC and DAC research programs, with licensing options available to access imec’s underlying IP portfolio.”