IEDM celebrates the 100th anniversary of the Field Effect Transistor (FET). . .

No other conference introduces so much leading work in this many different fields. The 71st annual IEEE IEDM conference will be held December 6-10, 2025 at the Hilton San Francisco Union Square hotel, with online access to recorded content available afterward.

Supporting the theme “100 Years of FETs: Shaping the Future of Device Innovations,” the 2025 IEDM technical program will consist of 295 presentations, plus a host of events that include Focus Sessions, Tutorials, Short Courses, an evening panel, a career luncheon, supplier exhibit and IEEE/EDS award presentations.

“This year's IEDM offers a preview of the next computing paradigm. We are witnessing the convergence of atomic-scale fabrication, 3D integration, and neuromorphic design, moving us beyond yesterday’s technology and even classical computing. From monolithic CFETs that redefine transistor density to in-memory computing that can mitigate the von Neumann bottleneck, more intelligent and more efficient technology is being built here,” said Gaudenzio Meneghesso, IEDM 2025 Publicity Chair, and Head of the Department of Information Engineering at the University of Padova (Italy).

“As AI is demanding unprecedented efficiency, the device community is rising to the challenge. IEDM 2025 showcases technologies that can power the next AI decade: from GaN chiplets for power delivery and silicon photonics for data transfer to 3D DRAM and FeFETs for in-memory computing. These device technologies will make the algorithms of tomorrow possible.”

“The pursuit of Moore's Law has evolved from a simple race to shrink transistors into engineering in multiple dimensions. IEDM 2025 showcases this new era: we are scaling up with 3D stacking like CFETs and 3D DRAM, scaling laterally with atomic-layer-deposited channel materials, and scaling past CPUs with novel architectures like in-memory computing,” said John Paul Strachan, IEDM 2025 Publicity Co-Chair, Director of Peter Grünberg Institute, Forschungszentrum Jülich, and Professor at RWTH Aachen University (Germany). “This is the culmination of a century of FET innovation, pushing the boundaries of what is physically possible to compute.”

Here are details of the 2025 IEEE International Electron Devices Meeting:

- Plenary Session Presentations – Monday, Dec. 8

- “Electron Device Challenges & Opportunities to Center AI Around the Individual Using Edge-Devices,” by PR “Chidi” Chidambaram, Senior Vice President & Fellow at Qualcomm

- “Inside Enterprise Mission-Critical Computing,” by Hillery Hunter, CTO, IBM Infrastructure & GM, Innovation; IBM Fellow at IBM

- “AI at the Edge,” by Dr. Ted Letavic, Senior Vice President, GlobalFoundries

- Tutorial Sessions – Saturday, Dec. 6

The Saturday tutorial sessions on emerging technologies are presented by experts in the field to bridge the gap between textbook-level knowledge and leading-edge current research, and to introduce attendees to new fields of interest. There are three time slots, each with two tutorials running in parallel:

1:30 p.m. - 2:50 p.m.

- Advances in CMOS Technologies and Cell Height Scaling Considerations, Yanbin Luo, Intel

- In-memory Computing Approaches for Large Language Model Acceleration, Manuel Le Gallo, IBM

3:05 p.m. - 4:25 p.m.

- Atomic-Layer-Deposited Atomically Thin In2O3 Transistors for BEOL Logic & Memory Applications, Peide Ye, Purdue University

- Quantum Computing – Concepts, Status Quo & Challenges Ahead, Hendrik Bluhm, RWTH Aachen University, Forschungszentrum Jülich, ARQUE Systems GmbH

4:40 p.m. - 6:00 p.m.

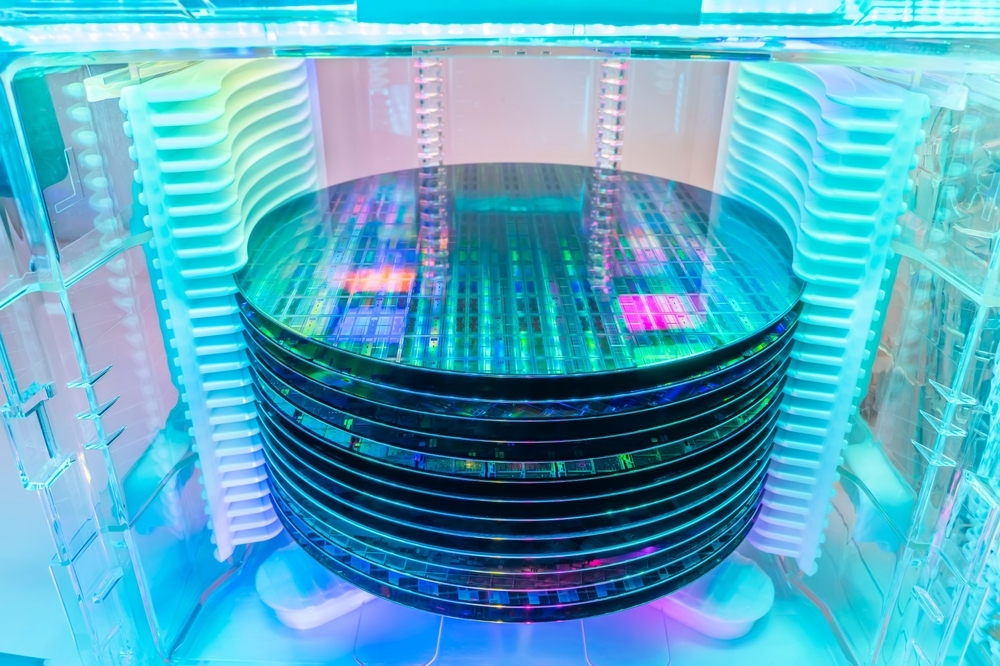

- Developing a Reliable & Open Chiplet Eco-System for Wafer-Scale Systems, Subramanian S. Iyer, UCLA

- High-Speed Memory Solutions for ML & High-Performance Compute, Yih Wang, TSMC

Short Courses – Sunday, Dec. 7

In contrast to the Tutorials, the full-day Short Courses are focused on different aspects of a single technical topic. They offer the opportunity to learn about important areas and developments, and to network with global experts.

Short Course 1: Advanced Logic & System Technologies in the AI Era, organized by Tenko Yamashita, IBM

- Device Technologies for GAA Scaling & Emerging Alternatives, Myunggil Kang, Samsung Electronics

- Advanced Interconnects Technologies for Cu Extension & Beyond, Koichi Motoyama, IBM

- Process Innovations & Materials to Sustain Moore’s Law in the Era of GAA & CFET, Nicolas Breil, AMAT

- Silicon Photonics for High-Speed, Energy-Efficient Data Transfer, Di Liang, University of Michigan

- Advanced Packaging & Chiplet Technologies for AI & HPC, James Chen, TSMC

- System Technology Co-Optimization (STCO) for Thermal Management & Power Delivery in Heterogeneous Integration, Kenneth Larsen, Synopsys

Short Course 2: Advanced Memory Technologies for Energy-Efficient AI & HPC, Organized by Duygu Kuzum, UC San Diego

- Memory-Centric AI Architectures Via Advanced Packaging & Heterogeneous Integration, Nuwan Jayasena, AMDBig AI for Small Devices, Hai Li, Duke University

- Exploring the Evolution of DRAM Technology: Operation Principles, Scaling Challenges, & the Emergence of HBM, Dae-hyun Moon, Samsung Electronics

- High-Density 3D Flash Memory in the CMOS Directly Bonded to Array (CBA) Era & Beyond, Katsuyuki Sekine, Kioxia

- Process & Material Innovations for Memory Scaling, Noboru Ooike, TEL

- Emerging Memory Technologies for Next-Generation AI & HPC Applications, Fabio Pellizzer, Micron

Luncheon – Tuesday, Dec. 9

A luncheon featuring leading industry experts presenting insights into today’s semiconductor industry. The luncheon will be moderated by Jan Hoentschel, IEDM 2025 General Chair and Director of Technology Development for CMOS devices at Global Foundries. The speakers are:

Hiroshi Iwai, Engineer, NYCU/Institute of Science Tokyo will present “A Century of Miracles: From the FET’s Inception to the Horizons Ahead.” From the FET’s invention a century ago to today’s ultra high-performance CMOS, the journey has been marked by a series of improbable coincidences leading to today’s technological miracles. This talk examines these extraordinary milestones and explores the next potential breakthrough that may once again define the FET’s limits of performance.

Bob Johnson, VP Analyst, Semiconductor & Electronics Technology Product Manager Research, Gartner will present “Semiconductor Market Outlook: Speedbumps on the Road to a Terrabuck?” As the semiconductor equipment market enters a period of strong growth mode driven by demand from AI, the next few years will not be business as usual. External forces are gathering on the horizon which will create opportunities for those who can anticipate and manage a challenging environment.

Evening Panel Session – Tuesday evening, Dec. 9

Held as an interactive forum where experts give their views on important industry topics, the IEDM evening panel is designed to foster an open exchange of ideas, with audience participation encouraged. This year’s panel will be moderated by John Wuu, Senior Fellow Design Engineer at AMD. It will focus on the theme, “100 Years of FETs: Looking Back & Looking Forward.”

When Julius E. Lilienfeld filed the patent for his Field Effect Transistor (FET) concept in 1925, decades before a working device could be built, few could have predicted the profound impact FETs would have a century later. Over the years, through countless innovations, FETs have demonstrated remarkable resilience and versatility. They have evolved in their topologies and materials and adapted to a wide array of applications from computing, memory, and storage to sensors, RF, and power management. To reflect on and celebrate the extraordinary journey of FETs through the last 100 years and to anticipate the exciting developments that lie ahead – this panel brings together experts from industry and academia, augmented by AI-driven insights, for a lively, thought-provoking discussion and debate.

Questions the panel will discuss include:

- What were the most important breakthroughs in the 100-year journey of FETs?

- Which emerging innovations are most likely to propel FETs forward?

- What role will AI play in advancing FET design, materials, and manufacturing?

- Or, as heterogeneous integration and advanced packaging gain prominence, will the importance of FETs diminish…or become even more central?

The panelists are:

- Serge Biesemans, Sr. Vice President, imec

- Daewon Ha, Vice President of Technology & Head of Advanced Device Research Lab, Samsung

- Chenming Hu, TSMC Distinguished Professor Emeritus, UC-Berkeley

- H.S. Philip Wong, Willard R. and Inez Kerr Bell Professor at Stanford, and TSMC

- ChatGPT – for AI input

Vendor Exhibition

A vendor exhibition will be held as part of IEDM.