New in-house application laboratory at the AP&S headquarters

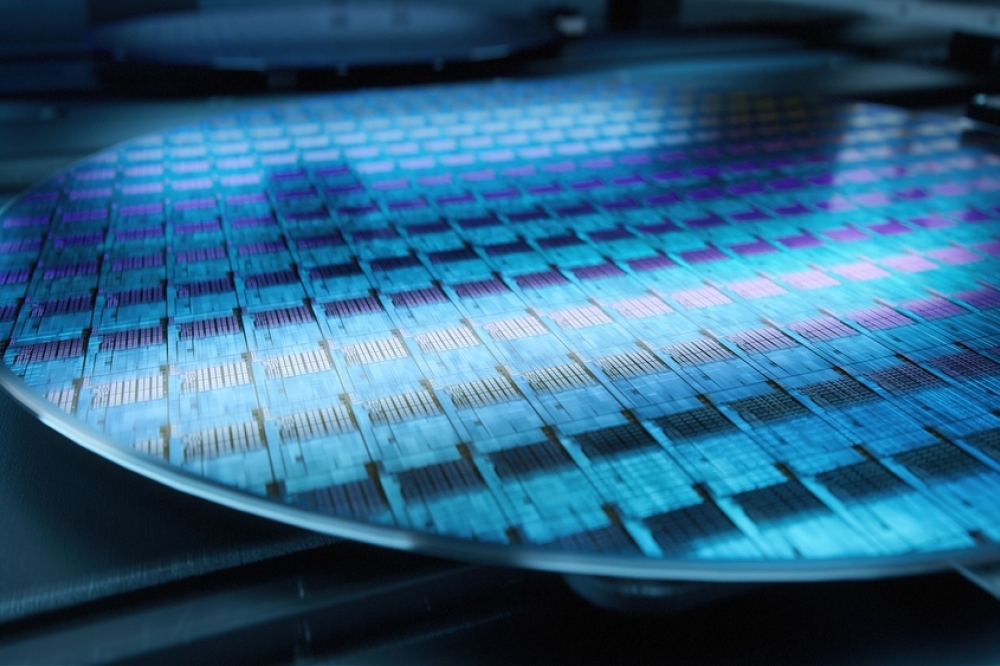

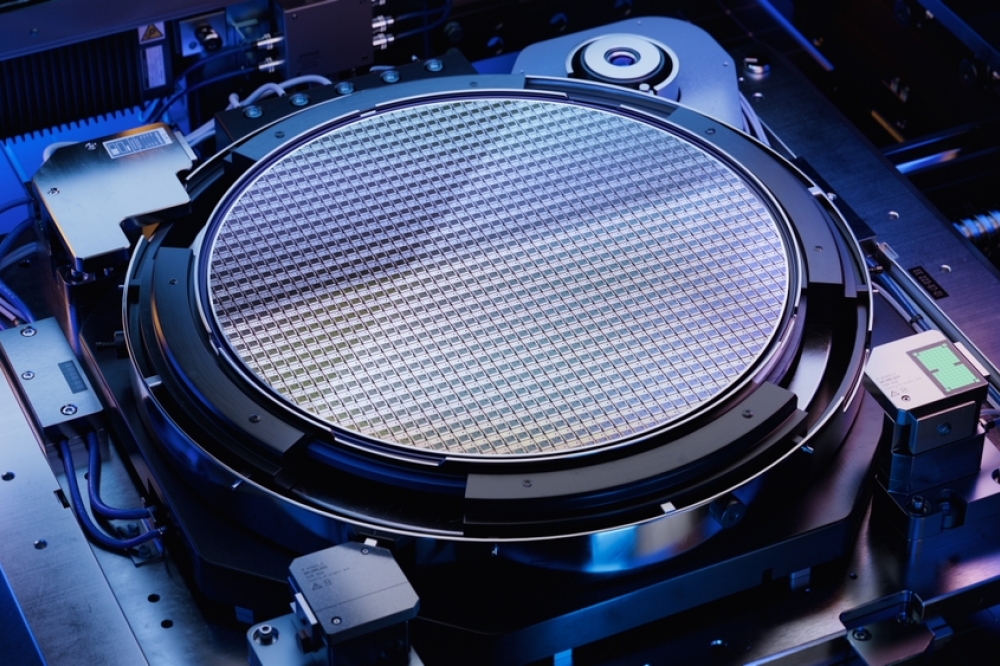

In 2016 AP&S International GmbH made significant investments in the expansion and modernization of its in-house laboratory. The size of the laboratory has almost tripled - originally 23 m³, now after the renovation it occupies an area of 66 m³. Since reopening in 2017 the new, modified laboratory, called Demo Center, welcomes customers from all over the world and offers them a variety of single wafer process demonstrations.

The purchase of a wet process application is a significant decision, in which many important aspects and complex contexts have to be considered. AP&S sees it as a mission to support customers efficient-ly during the decision making process to ensure they receive the perfect wet process solution, that meets their specific requirements. This happens in the Demo Center, where customers can test the wet process application, in which they are interested in and get all crucial information such as a com-prehensive test report containing complete parameters of the process set-up, a recommendation for the process recipe due to test results and further important system configuration details.

The Demo Center plays a significant role not only before the booking, but also during the production of the ordered application. Prior to the tool delivery, the Demo Center prepares all relevant steps for a quick tool commissioning and optimal production start-up. The range of services includes an in-house process evaluation with a definition of process parameters, a calculation of the throughput and chemi-cal consumption as well as trainings for customer's staff.

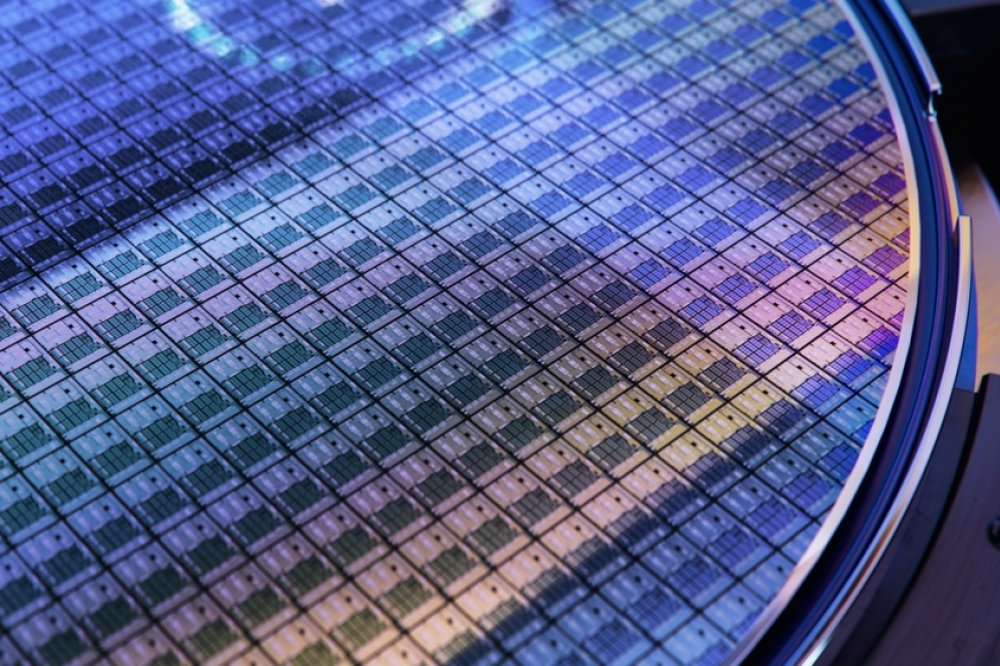

Available process demonstrations in the Demo Center are: advanced metal lift-off, metal etching, mask cleaning, photoresist development and strip as well as various cleaning processes. The following wafer sizes can be handled: Diameter (round substrates) up to 300 mm; Side length (square sub-strates) up to 9"; Thickness up to 10 mm. Possible chuck variations are low contact chucks, various vac-uum chucks as well as back- or frontside protection chucks. Different wafer materials with various thicknesses can be processed like Si, SiC, GaN, GaAg, Sapphire, Glass, etc. as well as Taiko wafers "“ other materials and substrate types are possible.