Chiplets increase performance and lower cost

Chiplet Summit announces its third annual event on January 21-23 at the Santa Clara Convention Center.

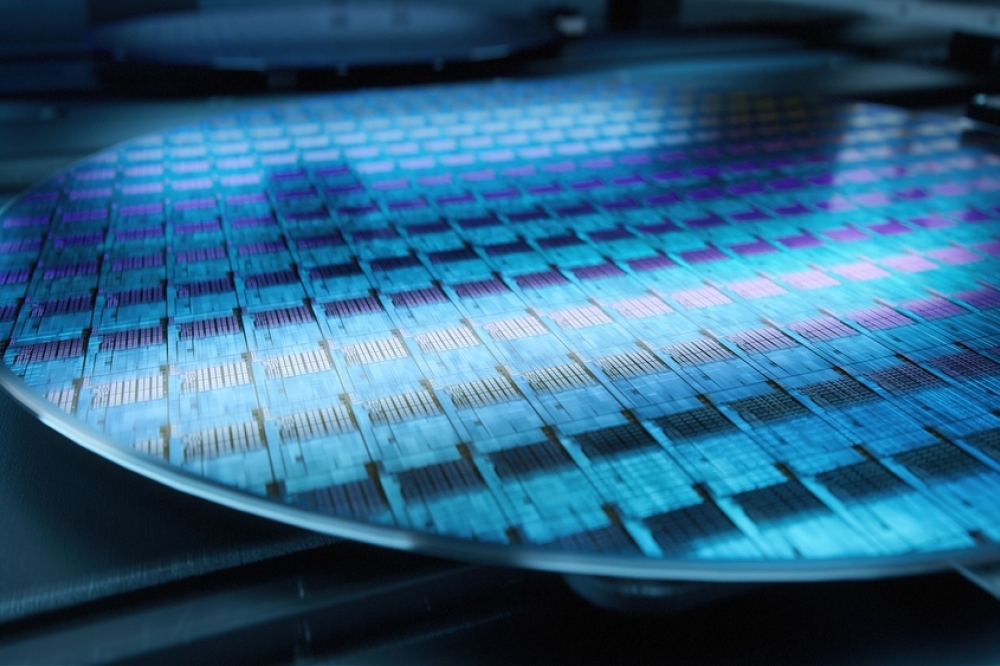

The 2025 meeting focuses on a new level in chip design: system-in- package (SiP). SiPs use advanced packaging to raise performance and reduce time-to-market. Co-optimization methods allow all design stages to proceed together. The event also covers supercomputer-in-a-package, a low-cost way to support generative AI.

The Summit features major vendor keynotes, expert tables, and technology and market updates. It also offers sessions on the open chiplet economy, die-to-die interfaces, and working with foundries. Designers will learn to develop leading-edge chips at low cost. An exhibit area will showcase the latest products.

“Chiplets help designers use the latest process nodes and packaging methods. They also allow faster updates and revisions,” said Chuck Sobey, Summit General Chair. He noted that “Specialists in all aspects of chip development will meet to ensure successful projects.”