A*STAR and Soitec announce Joint Program

Partnership to develop new layer transfer process for advanced packaging

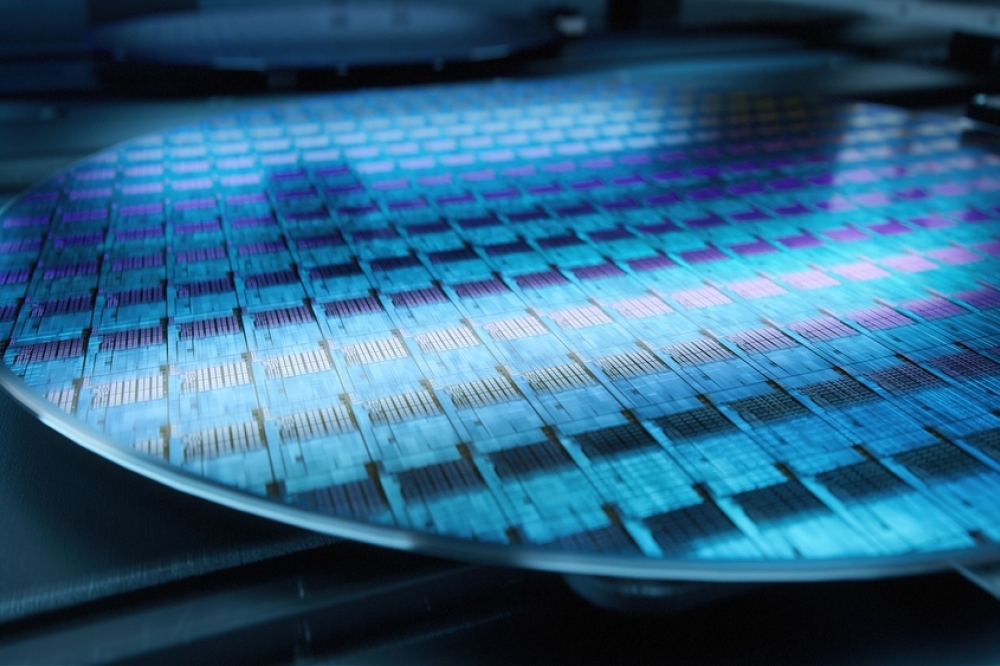

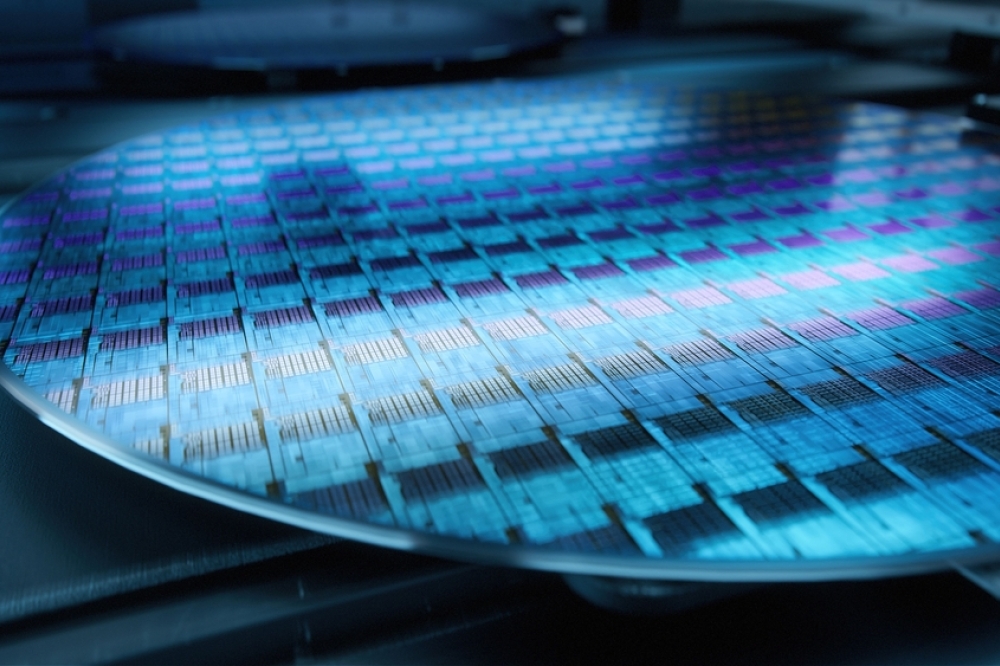

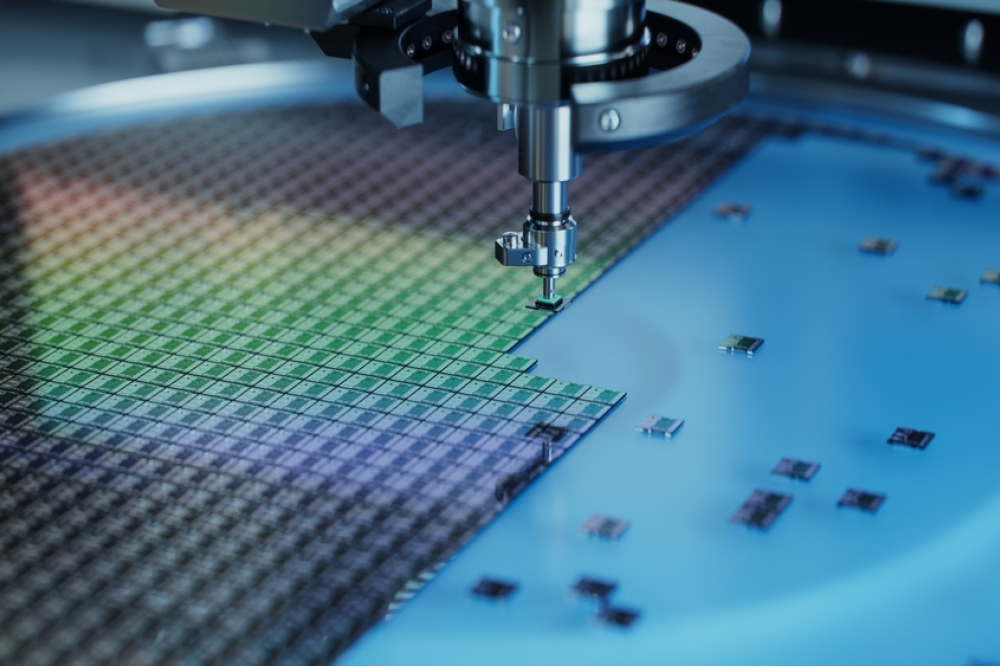

Singapore's Agency for Science, Technology and Research’s (A*STAR) Institute of Microelectronics (IME) and Soitec (Euronext Paris), a semiconductor materials firm, have launched a joint program to develop and integrate a new layer transfer process within advanced wafer level multi-chip packaging techniques.

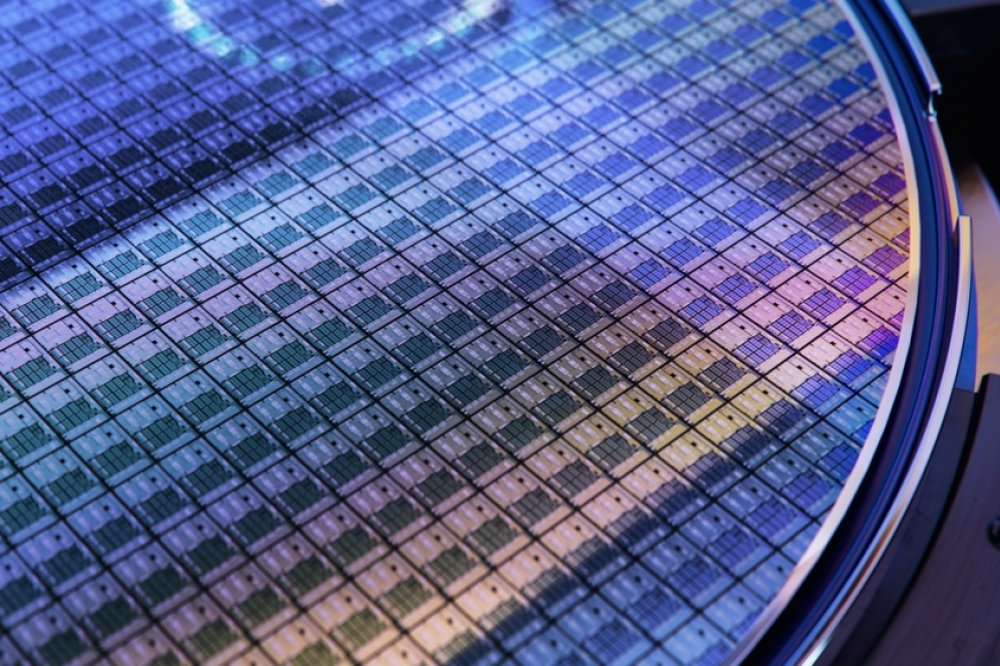

Based on the combination of IME’s Fan-Out Wafer Level Packaging (FOWLP) and 2.5D Through Silicon Interposer (TSI) technologies with Soitec’s Smart Cut technology, the new cost competitive process offers higher performance, energy efficiency and increased product yield.

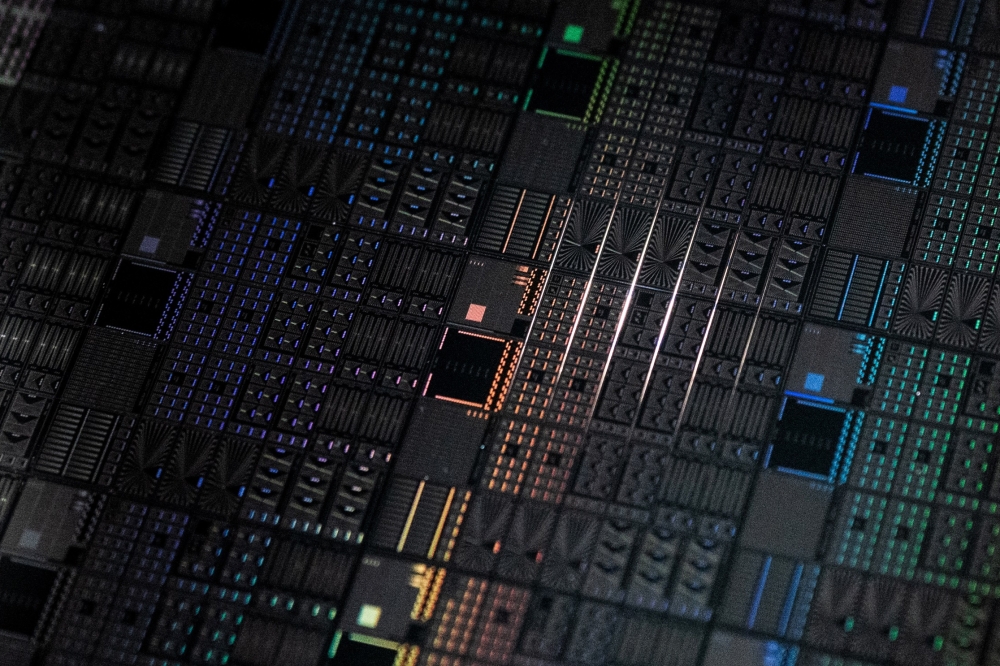

The rising complexity of today’s chips with growing numbers of smaller and smaller transistors and circuits requiring high I/O counts is driving collaborative innovation across the advanced packaging process community focused on identifying cost effective solutions for manufacturing, and increased data bandwidth to support hand-held, cloud and edge computing applications.

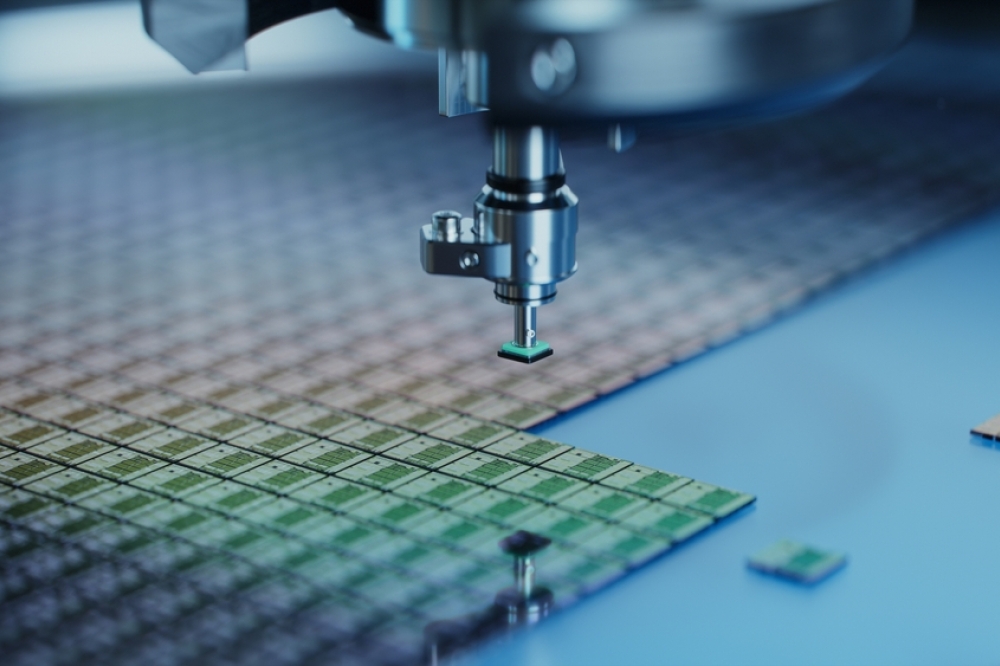

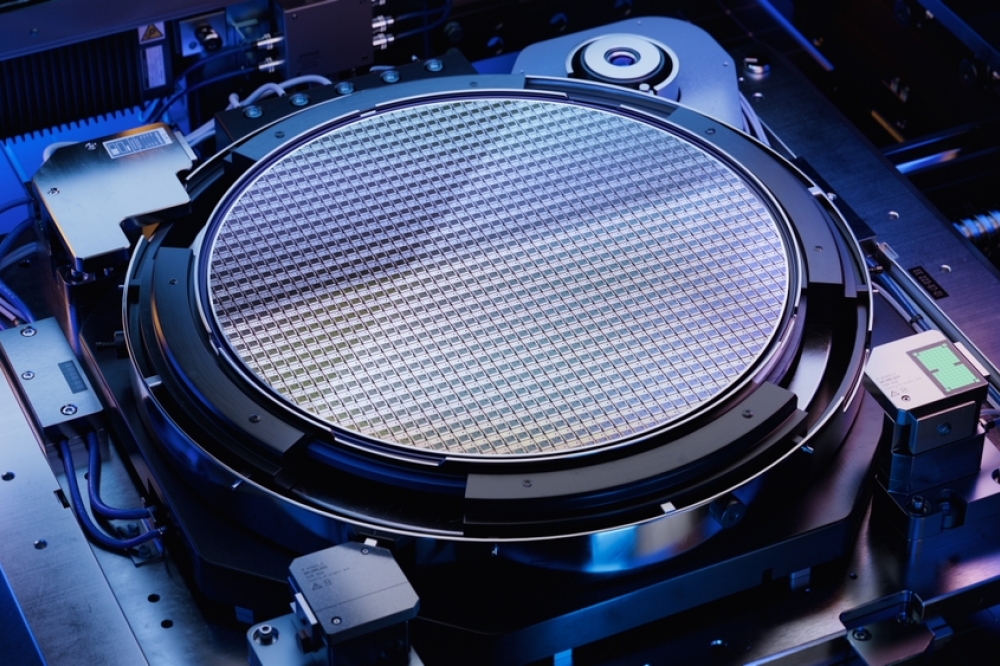

One of the standard processes in advanced packaging involves using a full silicon wafer for the layer transfer process, which can cost up to 3 cents/mm2. Soitec will partner with IME over the next three years to evaluate the use of its Smart Cut technology on IME’s advanced packaging platforms FOWLP and 2.5D TSI, with the objective to integrate a new layer transfer process as a key step in future generations of packaging techniques. This new process targets improved performance, lower power consumption and reduced production costs by eliminating the need to consume a full silicon wafer. IME will also conduct tests to evaluate the reliability and robustness of the newly developed process, which will help Soitec to determine its long-term viability.

Smart Cut technology makes use of both implantation of light ions and wafer bonding to define and transfer ultra-thin single-crystal layers from one substrate to another. It works like an atomic scalpel and allows active layers to be managed independently from the supporting mechanical substrate. Key benefits include the creation of multiple thin nanometric scale layers of virtually defect-free silicon by using low temperature bond and split techniques. These layers are then placed on top of active transistor circuitry. The thickness of the transferred layer can be determined with a high degree of precision by adjusting the implantation energy and process engineering. Transistors can then be completed using etch and deposition processes. Moreover, the donor substrate can be reused many times as the surface of the silicon wafer is repolished after each layer transfer operation, and the substrate can be reused.

Through this collaboration with Soitec, IME will provide advanced packaging expertise in architecture definition, modelling, design, process-integration, reliability-assessment and failure analysis. IME will execute the advanced packaging development in its fully functional, state of the art 300mm wafer level packaging, 2.5D/3DIC pilot line. IME’s end-to-end process capabilities and know-how in advanced FOWLP and 2.5D TSI will shorten development cycles and demonstrate cost-effective packaging solutions using Smart Cut technology. During the joint program, Soitec will contribute significant tool time, R&D personnel, and dedicated space in its clean room at its Pasir Ris fabrication facility in Singapore.

"Advanced packaging continues to be a bright spot in the high-value semiconductor market. We are excited to partner Soitec to develop packaging solutions that will contribute to the dynamic growth of this high-potential segment in Singapore and worldwide," said Dim-Lee Kwong, covering executive director, IME.

“Soitec and IME believe Smart Cut technology will deliver breakthrough results, revolutionising 2.5D/3D layer transfer process flow,” said Christophe Maleville, Soitec’s chief technology officer. “This strategic collaboration will not only develop a new Smart Cut application serving new generations of advanced packaging, but also open a brand-new market for Soitec beyond traditional engineered substrate manufacturing.”