Imec produces the first fully self-aligned, two-metal-level, semi-damascene module

Semi-damascene integration is an attractive, cost-effective approach to

extend interconnect process flows below 20nm metal pitch. Imec proposed

its approach five years ago, and now confirms the first experimental

demonstration of a functional, two-metal-level semi-damascene module at

18nm pitch.

BY GAYLE MURDOCH, TECHNICAL STAFF PRINCIPAL MEMBER AND ZSOLT TOKEI, IMEC FELLOW AND PROGRAM DIRECTOR FOR NANO-INTERCONNECTS

FOR MORE THAN 20 YEARS, copper (Cu) dual-damascene has been the workhorse process flow for building reliable interconnects. But when dimensional scaling continues and metal pitches become as tight as 20 nm and below, the

back-end-of-line (BEOL) increasingly suffers from RC delay, which is the result of a dramatically growing resistance-capacitance (RC) product. This has forced the interconnect community to start looking for alternative integration schemes and metals, with better figures of merit at tight metal pitches.

In this article, imec researchers Gayle Murdoch and Zsolt Tokei highlight the importance of via self-alignment at tight pitch, explain and demonstrate the key technical parameters of the module including via and line resistance as well as reliability. The results were presented at the 2022 IEEE VLSI Symposium on Technology and Circuits (VLSI 2022).

Figure 1: Imec’s semi-damascene flow: a) Ru etch (formation of the bottom local interconnect line (Mx)); b) gap fill; c) via etch; and d) via fill and top line (Mx+1) formation (as presented at VLSI 2022).

About five years ago, imec initially proposed semi-damascene as a viable alternative to Cu dual-damascene for integrating the most critical local (Mx) interconnect layers of the 1nm (and beyond) technology nodes.

Unlike dual-damascene, semi-damascene integration relies on the direct patterning of the interconnect metal for making the lines (referred to as subtractive metallization). No chemical mechanical polishing (CMP) of the metal is needed for completing the process flow.

The vias that connect subsequent interconnect layers are patterned in single-damascene fashion, then filled with metal and overfilled - meaning that the metal deposition continues until a layer of metal is formed over the dielectric. This layer of metal is then masked and etched to form the second interconnect layer with orthogonal lines.

After metal patterning, the gaps between the lines can be filled with a dielectric or can be used to form (partial) airgaps at the local layers. Note that in a semi-damascene flow, two layers (via and top metal) are formed in one-go, just like for conventional dual-damascene. This makes it effectively cost competitive, when benchmarked with dual-damascene (see figure 2).

Figure 2: Comparison of semi-damascene and dual-damascene cost at 18 nm metal pitch.

Benefits of a semi-damascene integration flow

Semi-damascene promises several advantages over Cu dual-damascene at tight metal pitches according to Zsolt Tokei, imec fellow and program director for nano-interconnects. “Firstly, it allows for higher line aspect ratios while keeping capacitance under control – promising an overall RC benefit. Secondly, the absence of a metal CMP step leads to a more simplified and cost-effective integration scheme.

Finally, semi-damascene integration requires a barrierless, patternable metal such as tungsten (W), molybdenum (Mo) or ruthenium (Ru). By using metals that, unlike Cu, do not require a metal barrier, the precious conductive area can be fully utilized by the interconnect metal itself. This ensures competitive via resistance at scaled dimensions.”

Besides the benefits there are of course numerous challenges to tackle before such a scheme would get industrial acceptance. One step in that direction is the actual demonstration of a two-metal-level scheme. While the benefits have so far only been showed through simulation and modelling, imec has for the first time provided experimental evidence with a two-metal-level semi-damascene module.

The fully self-aligned via – a critical building block

At metal pitches as tight as 20 nm, controlled via landing on top of the narrow lines is key to the successful operation of the semi-damascene integration module. When the via and the lines (at both via top and bottom) are not properly aligned, there is a risk of leakage between the via and an adjacent line. These leakage paths are the result of a too large overlay error induced by conventional patterning of the small via holes.

Gayle Murdoch, principle member of technical staff at imec said, “Finding a way for making functional, fully self-aligned vias has been a holy grail of the semi-damascene process. We achieved this milestone through intense collaboration between the integration, lithography, etch and cleaning groups at imec. With our fully-self aligned integration scheme, we were able to compensate for overlay errors up to 5 nm – a key achievement.”

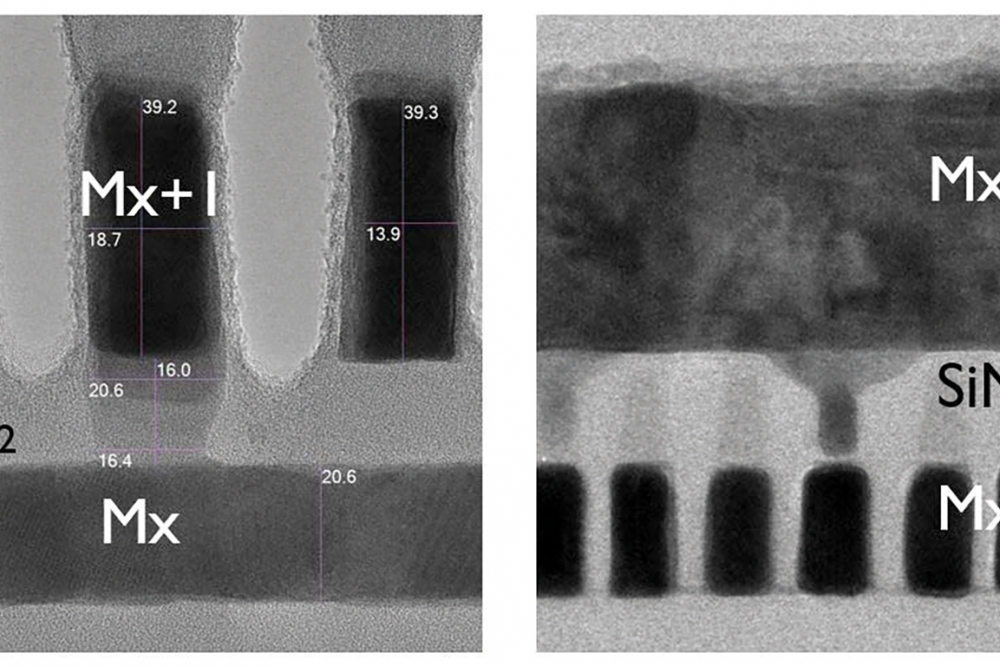

Bottom self-alignment was ensured by the selective removal of silicon nitride after gap fill, allowing the via to form on the confines of the lower metal line. The self-alignment towards the top metal layer (Ru) was achieved by the Ru over-etch step, applied after via overfill and Ru patterning.

Figure 3: Self-aligned via along Mx (left) and across Mx (right). The X-TEMs show self-aligned vias landing on 18 nm pitch Ru lines (as presented at VLSI 2022).

New milestone: Good resistance and reliability at 18 nm pitch

Using subtractive etch of Ru with fully self-aligned vias resulted in a functional two-metal level device at 18nm metal pitch. EUV lithography combined with self-aligned double patterning (SADP) was used for patterning the 9nm ‘wide’ Ru bottom local interconnect line (Mx), while single-exposure EUV lithography was used for printing the top line (Mx+1) and via. The top metal was combined with air gaps to counter the capacitance increase.

When benchmarking the line resistance vs. conducting area of Ru against Cu, Ru clearly outperforms Cu for the target metal pitches. Via self-alignment was confirmed both morphologically and electrically. Excellent via resistance was achieved (ranging between 40 and 60 Ω for 26-18 nm metal pitch), and a via-to-line breakdown field of >9MV/cm was demonstrated.

Zsolt Tokei remarked, “We have demonstrated excellent values for all the key technical parameters, including via and line resistance and reliability. This shows that semi-damascene is a worthy alternative to dual-damascene for integrating the first three local interconnect layers of the 1nm technology node and beyond. Our two-metal-level device with fully self-aligned via has proven to be a key building block.”

The researchers said that they believe further improvements are possible by increasing the aspect ratio of the lines (which reduces resistance) while keeping the air gaps (which keeps capacitance under control). At the same time, imec has concrete ideas for implementing middle-of-line (MOL) and BEOL technology boosters using the semi-damascene technology (which allows further area reduction at standard cell level).

Figure 4: Conductive area vs. line resistance for Ru and Cu lines (as presented at VLSI 2022).

Authors

Gayle Murdoch graduated from the University of Edinburgh in 1997 with an Honours degree in Chemical Physics. She began her career in the UK semiconductor manufacturing industry, first at NEC Semiconductors as a lithography engineer, and later joining Filtronic Compound Semiconductors where she worked on etching development and integration for GaAs devices, eventually becoming lead etch engineer. In 2008 she joined imec’s Advanced Lithography team, before moving to BEOL Integration in 2013. She has worked on a range of topics including low k dielectric integration, fully self aligned vias, and most recently, semidamascene integration. She currently holds the position of Principle Member of Technical Staff and leads the BEOL Integration team.

Zsolt Tokei is imec fellow, program director nano-interconnects at imec. He joined imec in 1999 and since then held various technical positions in the organization. First as a process engineer and researcher in the field of copper low-k interconnects, then he headed the metal section. Later he became principal scientist, and program director nano-interconnects. He earned a M.S. (1994) in physics from the University Kossuth in Debrecen, Hungary. In the framework of a co-directed thesis between the Hungarian University Kossuth and the French University Aix Marseille-III, he obtained his PhD (1997) in physics and materials science. In 1998 he started working at the Max-Planck Institute of Düsseldorf, Germany, as a post-doctorate researcher. Joining imec, he continued working on a range of interconnect issues including scaling, metallization, electrical characterization, module integration, reliability and system aspects.