Accelerating automotive AI software development and evaluation

Renesas Electronics has launched a new cloud-based development environment aimed at streamlining the software design process for automotive AI engineers.

The new platform, AI Workbench, is an integrated virtual development environment that empowers automotive AI engineers to design, simulate and fine-tune their automotive software - all within the cloud.

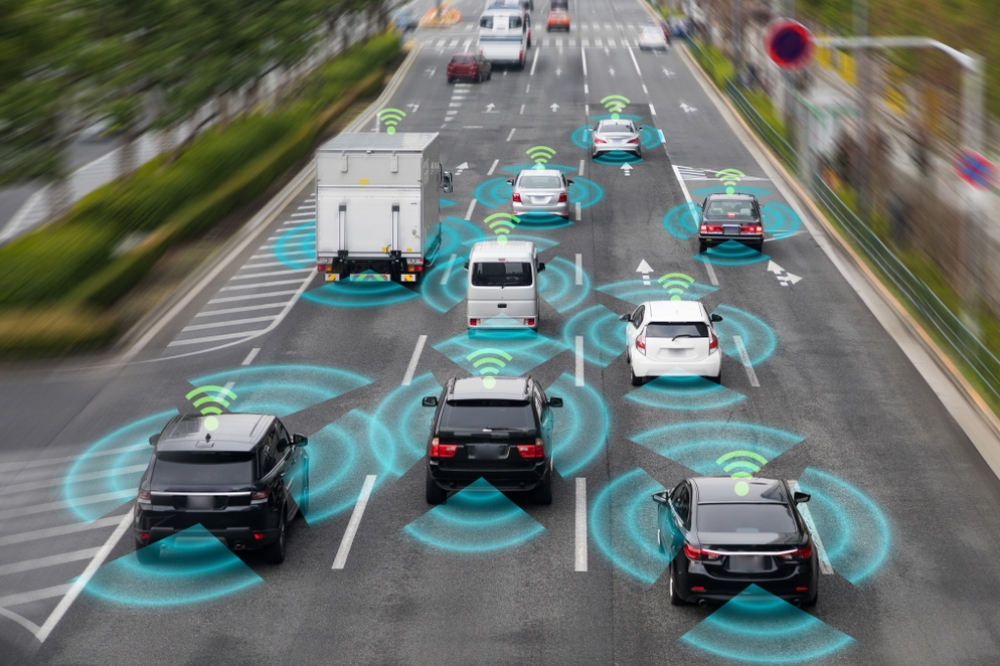

With this environment, engineers can immediately begin designing automotive software by leveraging Microsoft Azure services including Azure Compute, IaaS services, Microsoft Entra ID and Azure Security. Instead of installing tools on a PC or obtaining an evaluation board, they can perform tasks such as performance evaluation, debugging and verification using simulation tools online. This approach aligns with the "Shift-Left" approach, which enables software creation and testing earlier in the design cycle, even before the actual hardware becomes available. For example, it is possible to start developing AI-enabled application software to support ADAS (Advanced Driver Assistance System) and autonomous driving for the upcoming fifth-generation R-Car System on Chip (SoC) prior to the availability of hardware samples. This environment will serve as a unified development platform for designing and testing Renesas’ scalable automotive SoCs and microcontrollers (MCUs), regardless of product type or application.

“We are thrilled to introduce a cloud-based virtual development and AI model performance testing environment for automotive AI engineers in collaboration with Microsoft, a leading cloud technology provider," said Mandali Khalesi, Global VP, HPC AI and Cloud Technology at Renesas. “We are committed to improving the AI development environment through new features such as continuous monitoring and analysis of software usage.”

“Cloud-based development is a secure and cost-effective method to address the increasing complexities of today’s embedded projects. The collaboration between Renesas and Microsoft aims to tackle this challenge and accelerate the digital transformation of the automotive industry,” said Ulrich Homann, Corporate Vice President & Distinguished Architect, Cloud + AI, Microsoft. “With Renesas’ AI Workbench, developers can now efficiently build and test software for a myriad of applications using Renesas SoCs in a cloud-based environment powered by Azure."

The AI Workbench includes the following four functional blocks today. Renesas plans to enhance its offering in the future with additional features such as selected functionality or customization options tailored to support various development processes.

1. Upgraded AI Compiler Toolchain

Renesas will upgrade its SoC AI compiler toolchain with a novel “Hybrid Compiler (HyCo)” architecture and make it available through the AI Workbench. The new HyCo architecture developed in house and kernel libraries will allow engineers to unlock broader AI model and ONNX operator coverage, beyond the coverage of existing-third party hardware accelerator compilers available on Renesas SoC such as DSPs and NPUs.

2. AI Model Performance Testing Environment

Renesas will provide NNPerf, an online test environment for developers to evaluate the performance of AI models running on live Renesas SoCs with an updated hybrid AI compiler. Testing will run on real hardware in Renesas’ global device farm, without the need for evaluation boards. With the ability to batch code programs, perform real-time inference tests, and compare performance across different AI models, application engineers can estimate and make decisions on tradeoffs between models, memory footprints, latency and more.

3. Software Development Environment

Microsoft's code editor, Visual Studio Code (VSCode) and a software development kit (SDK) from Renesas are both available in the cloud. Using the tool suite, developers can launch their development environment in the cloud in a matter of minutes. Developers can customize their independent development environment and perform all design work using just a web browser on their PC.

4. Software Evaluation/Verification Environment

Renesas will also provide an environment for developers to test and verify their application software using the AI models defined in the AI model performance testing tool NNPerf. This includes simulators such as SILS (Software in the Loop Simulator), and HILS (Hardware in the Loop Simulator), allowing users to verify the operation designed for their specific AI application.