Marvell introduces 2nm platform for accelerated infrastructure silicon

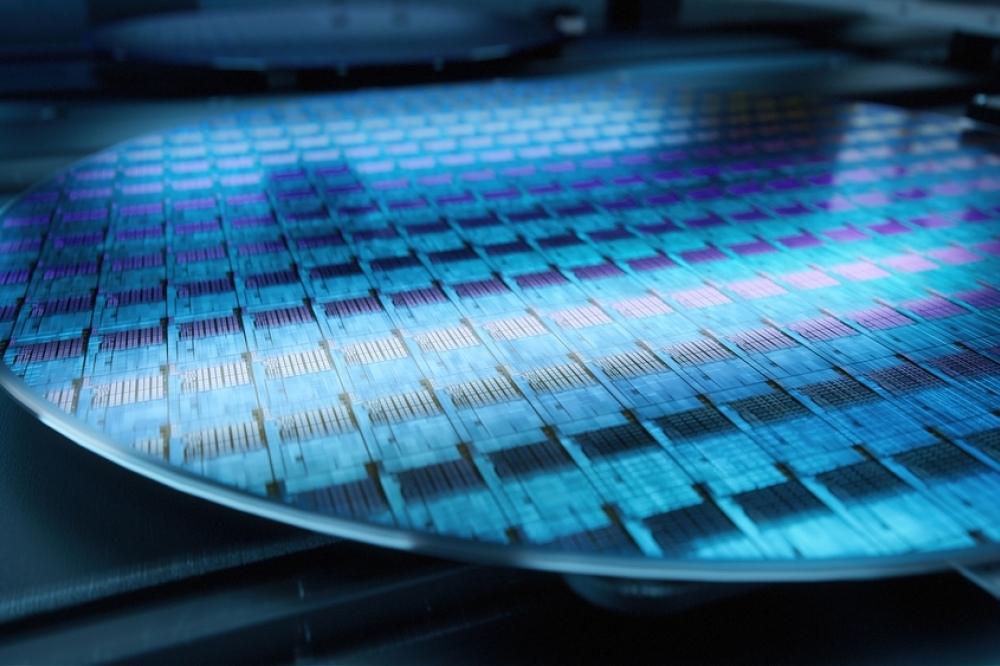

Marvell extends its longstanding partnership with TSMC to 2nm manufacturing.

Marvell Technology is extending its collaboration with TSMC to develop what is said to be the industry's first technology platform to produce 2nm semiconductors optimized for accelerated infrastructure.

Behind the Marvell 2nm platform is the company's industry-leading IP portfolio that covers the full spectrum of infrastructure requirements, including high-speed long-reach SerDes at speeds beyond 200 Gbps, processor subsystems, encryption engines, system-on-chip fabrics, chip-to-chip interconnects, and a variety of high-bandwidth physical layer interfaces for compute, memory, networking and storage architectures. These technologies will serve as the foundation for producing cloud-optimized custom compute accelerators, Ethernet switches, optical and copper interconnect digital signal processors, and other devices for powering AI clusters, cloud data centers and other accelerated infrastructure.

Investing in platform components like interconnects and advanced packaging is imperative for accelerated infrastructure: breakthroughs at the platform level alleviate data bottlenecks that can hinder performance of the entire system as well as reduce the cost and time-to-market for multichip solutions geared at running the most complex applications.

"Tomorrow's artificial intelligence workloads will require significant and substantial gains in performance, power, area, and transistor density. The 2nm platform will enable Marvell to deliver highly differentiated analog, mixed-signal, and foundational IP to build accelerated infrastructure capable of delivering on the promise of AI," said Sandeep Bharathi, chief development officer at Marvell. "Our partnership with TSMC on our 5nm, 3nm and now 2nm platforms has been instrumental in helping Marvell expand the boundaries of what can be achieved in silicon."

"TSMC is pleased to collaborate with Marvell in pioneering a platform for advancing accelerated infrastructure on our 2nm process technology," said Kevin Zhang, senior vice president of business development at TSMC. "We are looking forward to our continued collaboration with Marvell in the development of leading-edge connectivity and compute products utilizing TSMC's best-in-class process and packaging technologies."

Marvell moved from being a fast follower to a leader in bringing advanced node technology to infrastructure silicon with its 5nm platform. Marvell followed the achievement with several 5nm designs and the first portfolio for infrastructure silicon on TSMC 3nm processes.

"We take a modular approach to semiconductor design R&D, focusing first on qualifying foundational analog, mixed-signal IP and advanced packaging that can be used across a broad spectrum of devices," Bharathi said. "This allows us to bring innovations such as process manufacturing advances faster to market."