Adeia wins ECTC Award for paper on “Fine Pitch Die-to-Wafer Hybrid Bonding”

Adeia Inc., a leading research and development and intellectual property licensing company known for bringing innovations in the semiconductor and media technology sectors to market, was awarded Best Session Paper at the 2024 Electronic Components and Technology Conference (ECTC) held in Denver, Colorado on May 28-31, 2024.

“It achieves this by facilitating higher interconnect density than alternatives like micro-bumps, thereby improving bandwidth and lowering latency. Higher density of interconnections between the memory die and logic chip improves performance and efficiency while offering better thermal connectivity.”

Dr. Thomas Workman, senior principal engineer for Adeia and author of the paper, received the award for “Fine Pitch Die-to-Wafer Hybrid Bonding,” which explores the range of parameters associated with implementing hybrid bonding technology in high-volume manufacturing processes.

“As adoption of hybrid bonding accelerates, there is rising demand for practical information and guidance on implementing the technology in high volume manufacturing. This paper provides a detailed pathway for manufacturers to understand the parameters, limitations and yield considerations of hybrid bonding, ultimately enabling industry leaders to successfully implement the technology in their own processes,” said Dr. Workman.

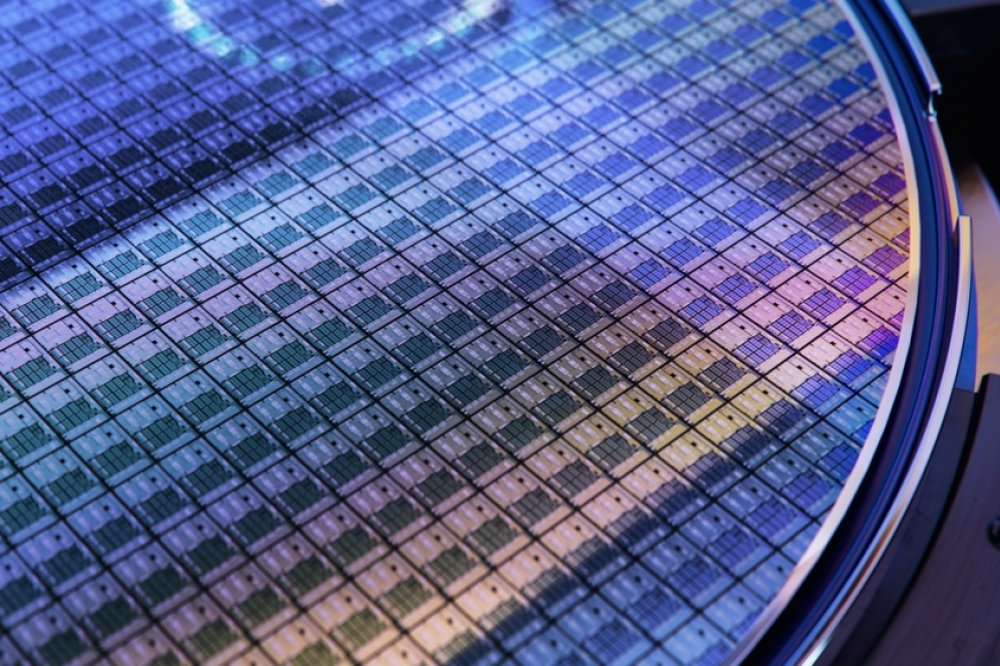

Hybrid bonding technology in advanced 2.5 and 3D packaging has rapidly gained traction in the semiconductor industry to enhance performance and scalability. Advanced packaging architectures integrate multiple semiconductor components into a single package or module to create functional systems. Within the package or module, a chip-to-chip interconnect is formed with hybrid bonding to deliver the highest bandwidth with low latency.

Hybrid bonding represents a significant advancement in semiconductor technology, particularly in terms of performance per watt.

“By enabling faster processing within established thermal limits, hybrid bonding enhances efficiency and reduces energy consumption,” explained Dr. Workman. “It achieves this by facilitating higher interconnect density than alternatives like micro-bumps, thereby improving bandwidth and lowering latency. Higher density of interconnections between the memory die and logic chip improves performance and efficiency while offering better thermal connectivity.”

Looking ahead, Dr. Workman stated that hybrid bonding is gaining increasing traction in high-volume manufacturing applications. Interest and activity in hybrid bonding are expected to grow as progress is made in shrinking the pitch to a submicron level.

“This would allow hybrid bonding to be a solution for an even wider range of applications. The next step is demonstrating how hybrid bonding can be implemented with standard equipment and processes. This will expand the practical opportunities to leverage the full benefits of this technology,” he concludes.

With over 20 years of experience in process and equipment engineering, Dr. Workman has successfully launched and managed fabrication and assembly lines for semiconductors, photonics, solar cells and nanotechnology. He is known for his excellent problem-solving skills as well has his deep knowledge of materials and manufacturing systems.