ACM Research reveals major performance breakthrough

Enhanced cleaning performance for advanced chip manufacturing. Significant chemical savings and environmental benefits.

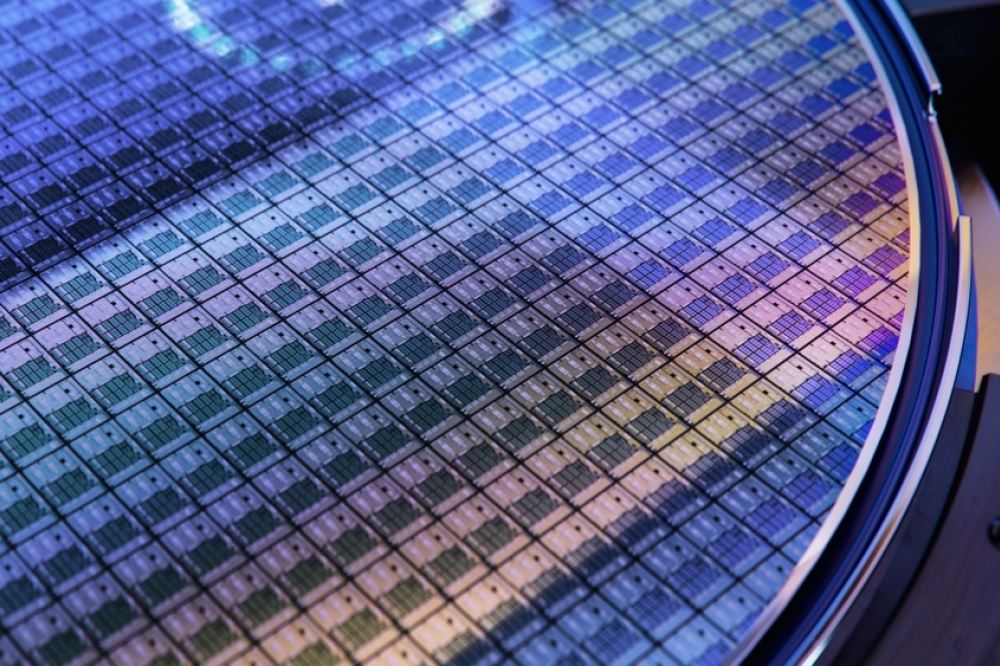

ACM Research has announced a major performance breakthrough for its flagship Ultra C Tahoe Cleaning tool. The resulting enhancements are designed to meet demanding technical requirements of advanced nodes for foundry, logic and memory applications.

The Ultra C Tahoe now achieves the performance of standalone single-wafer cleaning tools on low-to-medium temperature sulfuric peroxide mix (SPM) processes. Tahoe’s patented hybrid architecture is among the first in the industry to combine batch wafer processing and single wafer cleaning chambers into the same SPM tool. The hybrid architecture delivers enhanced cleaning performance, high throughput, and process flexibility, with up to 75% reduction in chemical consumption. ACM estimates cost savings of up to $500,000 per year from sulfuric acid alone, with additional environmental and cost benefits from reduced sulfuric acid treatment and disposal.

“With the rise of AI to the forefront of consumers’ minds, we expect increased public attention on the environmental impact of semiconductor chip manufacturing. We believe ACM’s Ultra C Tahoe is well-positioned to help customers increase production of advanced AI chips, but with a reduced footprint on the environment,” said Dr. David Wang, ACM’s President and Chief Executive Officer.

“We believe the Ultra C Tahoe is another example of excellence from ACM’s innovative and world-class R&D team,” Dr. Wang added. “We believe the Tahoe platform is well-positioned to capture market share within the SPM market, particularly in middle and low-temperature applications, which believe represents an estimated 20% of the total clean market.”

The upgraded Ultra C Tahoe is now in production at several high-volume customer facilities in mainland China. Additional logic and memory customers are evaluating the tool, and we expect to deliver additional production units through the end of 2024.

New Features and Benefits of the Upgraded Ultra C Tahoe Tool:

Enhanced Particle Removal: The Tahoe platform’s advanced cleaning capabilities have achieved average particle counts of less than 6 particles at 26nm, meeting the stringent requirements for advanced node manufacturing. The tool is also capable of removing 1x nm particles for the most advanced logic and memory applications, with the addition of a smaller particle filtering system.

Higher Throughput: The upgraded 25-slot bench module (previously 13 slots) and nine single-wafer chambers (upgraded from eight) now deliver throughput exceeding 200 wafers per hour, comparable to the capacity of a 12-chamber SPM system.

Environmental and Cost Benefits: With a reduction of up to 75% in sulfuric acid consumption, the Ultra C Tahoe aligns with environmental regulations and sustainability goals, reducing costs for high-volume manufacturers.

Expanded Process Capabilities: Qualified for more than 30 production layers, including key loops such as lightly-doped drain (LDD) and source/drain (SD), with additional layers and applications currently in development.

Advanced Flexibility in Single-Wafer Cleaning: Optional configurations include new jet spray technology, ACM’s patented SAPS/TEBO technologies, and HOT IPA drying technology, increasing the tool’s versatility across multiple process applications.