Imec unveils imec.kelis

The AI datacenter landscape is undergoing rapid transformation. As workloads scale to trillions of parameters and energy demands surge, system architects face mounting pressure to balance performance with sustainability and cost. Traditional simulation methods are often slow, opaque, or too narrow in scope. Imec.kelis addresses this gap by offering a fast, transparent, and validated modeling framework that enables informed decision-making across the full stack—from chip to datacenter. It empowers teams to explore architectural trade-offs, optimize resource allocation, make informed decisions, and accelerate innovation in a field where time-to-insight is critical.

Imec.kelis provides an end-to-end framework for evaluating system performance across compute, communication, and memory subsystems. It is tailored for large language model (LLM) training and inference workloads, offering fast, accurate, and generalizable predictions validated on industry-standard platforms such as Nvidia A100 and H100. The tool builds on imec’s proven track record in analytical performance modeling for high-performance computing (HPC) and artificial intelligence (AI). It leverages imec’s system-level modeling and performance analysis for compute, communication, and memory subsystems, especially in the context of large-scale AI datacenters and large language model (LLM) workloads, imec’s hardware-software- codesign expertise, and semiconductor technology roadmap.

“Imec.kelis is more than a simulator—it’s a strategic enabler for the next generation of AI infrastructure,” said Axel Nackaerts, imec’s System Scaling lead. “By combining hardware-software- codesign, we empower system architects to make informed decisions at datacenter scale.”

Key Features:

• LLM task-graph analyzer and parallelism mapper

• Hierarchical roofline model and topology-aware communication library

• Interactive dashboard for real-time design space exploration

• Validated within 12% error margin for large-scale LLM

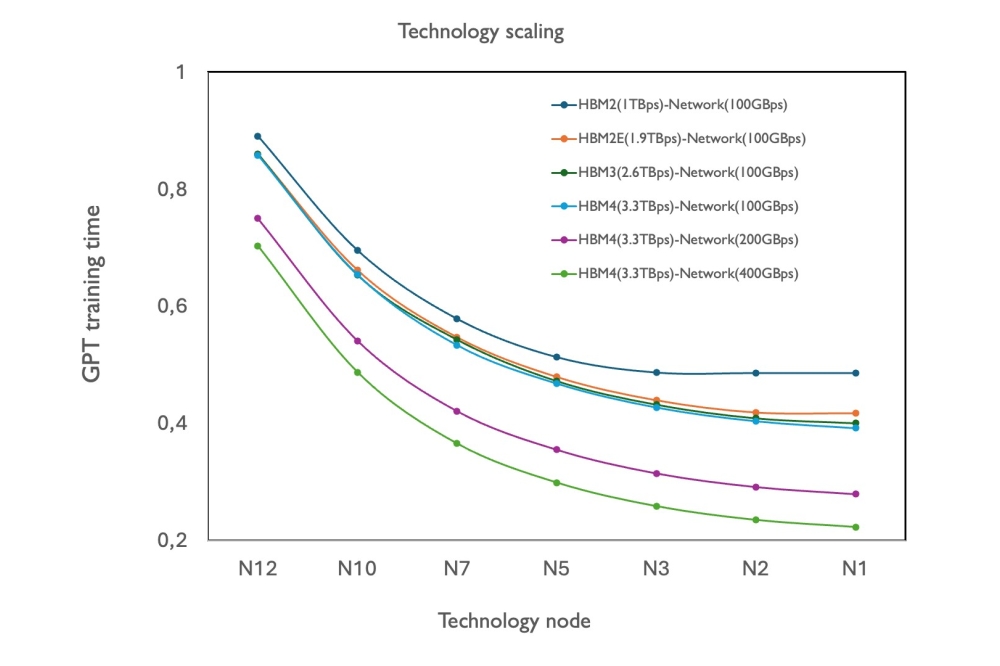

"In a test case, we used imec.kelis to compare the performance (defined as training time for GPT3), for different GPU architectures and scaling nodes, at plotted performance against cost, showcasing the flexibility of the tool for various purposes, such as architecture exploration, future technology projection, and co-optimization. Our results show that imec.kelis enables careful validation of performance and helps identify key insights for architecture exploration and future technology projection.” stated Nackaerts.

Imec.kelis v1.0 will be available for licensing starting Q1 2026. The tool has already attracted early adopters, signaling strong market interest.