Siemens and ASE introduce enablement technologies for high density advanced package designs

The OSAT Alliance program helps promote the adoption, implementation, and growth of HDAP throughout the semiconductor ecosystem and design chain, enabling system and fabless semiconductor companies to have a friction-free path to emerging packaging technologies.

Siemens Digital Industries Software has announced that its collaboration with Advanced Semiconductor Engineering, Inc. (ASE) has generated two new enablement solutions engineered to help mutual customers create and evaluate multiple complex integrated circuit (IC) package assemblies and interconnect scenarios in an easy-to-use, data-robust graphical environment prior to and during physical design implementation.

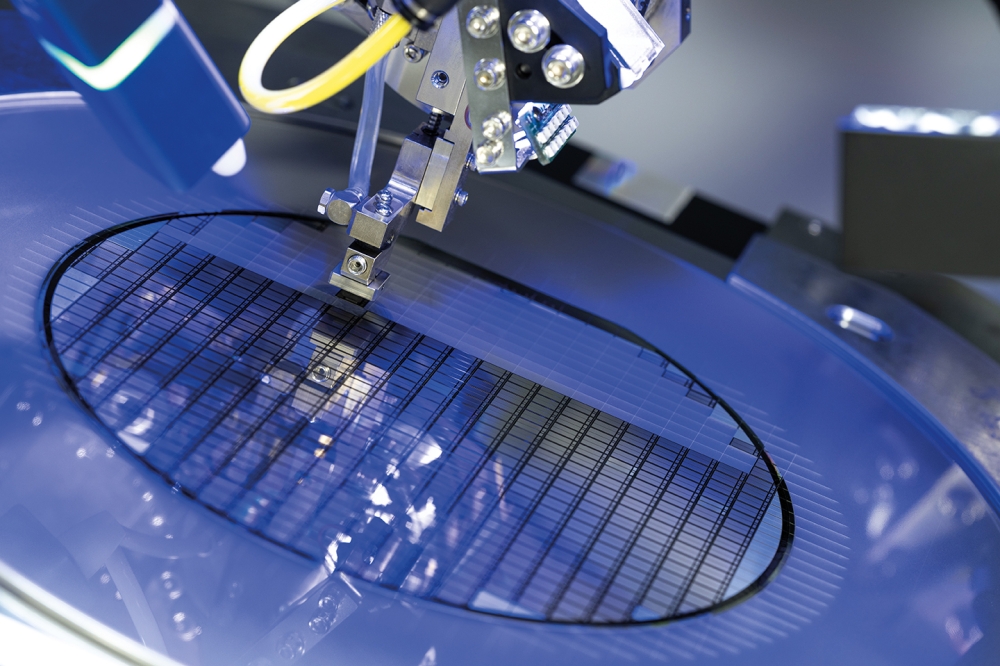

The new high-density advanced packaging (HDAP) enablement solutions stem from ASE’s participation in the Siemens OSAT Alliance – a program designed to drive faster adoption of new HDAP technologies like 2.5D, 3D IC and Fan-Out wafer-level packaging (FOWLP) for next-generation IC designs. ASE is a leading provider of independent semiconductor assembling and test manufacturing services.

ASE’s latest achievements as part of the OSAT Alliance include an assembly design kit (ADK) that helps customers using ASE’s Fan Out Chip on Substrate (FOCoS) and 2.5D Middle End of Line (MEOL) technologies to fully leverage the Siemens HDAP design flow. ASE and Siemens have also agreed to extend their partnership to include the future creation of a single design platform from FOWLP to 2.5D substrate design. All of these joint initiatives leverage Siemens’ Xpedition Substrate Integrator software and Calibre® 3DSTACK platform.

“By adopting the Siemens Xpedition Substrate Integrator and Calibre 3DSTACK technologies, and through integration with the current ASE design flow, we can now leverage this mutually developed flow to significantly reduce 2.5D/3D IC and FOCoS package assembly planning and verification cycle times by about 30 to 50 percent in each design iteration,” said Dr. C.P. Hung, vice president, ASE Group. “Through the comprehensive design flow, we can now more quickly and easily co-design with our customers for 2.5D/3D IC and FOCoS design and close any physical verification issues for their entire wafer package assembly.”

The OSAT Alliance program helps promote the adoption, implementation, and growth of HDAP throughout the semiconductor ecosystem and design chain, enabling system and fabless semiconductor companies to have a friction-free path to emerging packaging technologies. The alliance helps enable mutual customers to fully leverage the Siemens HDAP flow and quickly bring to market innovations for internet of things (IoT), automotive, 5G network, artificial intelligence (AI) and other fast-growing IC applications.

“We are pleased that ASE continues to develop highly innovative IC packaging solutions as part of our OSAT Alliance,” said AJ Incorvaia, senior vice president and general manager, Electronic Board Systems Division, Siemens Digital Industries Software. “In doing so, and by providing a fully validated ADK for ASE’s leading-edge FOCoS and 2.5D MEOL technologies, we expect to enable customers to more easily transition from classic chip designs to 2.5D, 3D IC, and Fan-Out solutions.”

For more information about the OSAT Alliance program, please visit https://www.mentor.com/pcb/ic-packaging/osat-alliance.