Renesas and Matsushita develop technique for stabilizing Sram manufacture

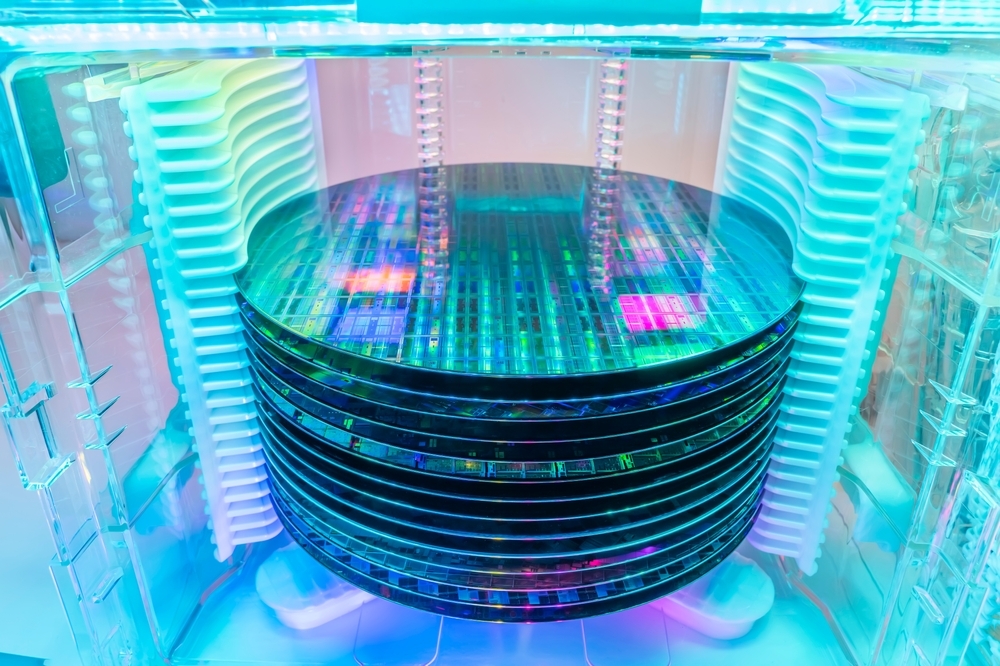

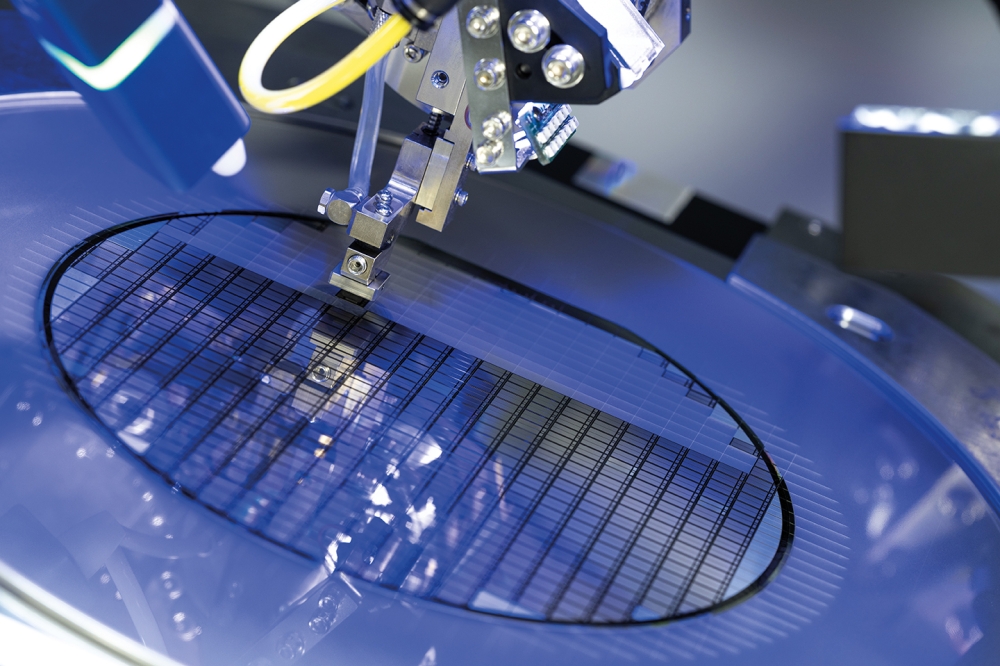

Renesas Technology Corp. and Matsushita Electric Industrial Co., Ltd. have announced the development of a technique that achieves stable operation with 45nm (nanometer) process generation bulk CMOS for SRAM (Static Random Access Memory) that can be embedded in SoC (system-on-a-chip) devices and microprocessors (MPUs).

Tests of experimental chip with 512-Kbit SRAMs employing this technique have confirmed stable operation over a wide temperature range (-40?C to 125?C) and a larger operating voltage range margin with respect to process variations. The experimental SRAM chip, produced using a 45nm CMOS process, incorporated two different memory cell designs, one with a cell area of both 0.327µm2 and another with a cell area of only 0.245µm2 (the smallest level available). The smaller memory cell was achieved with a reduced processing dimension margin.

The innovation is of considerable significance because SRAM is an essential on-chip function for SoCs and MPUs used in embedded control applications. Conflicting trends see those applications becoming more sophisticated, requiring more SRAM, even as semiconductor process shrinks are making it more difficult to produce the stable SRAM operation necessary for proper device functionality. The 45nm process generation SRAM enabled by the new fabrication technique will make it possible to implement high-performance chips at low cost because it uses bulk CMOS instead of Silicon-on-Insulator (SOI) material, the more expensive alternative.

As LSI fabrication processes become finer, the increasing miniaturization causes greater variations of transistor characteristics, especially threshold voltage (Vth), which can disrupt SRAM operation. Vth variation takes two forms. Global Vth variation occurs on a chip-by-chip or wafer-by-wafer basis due to minute disparities in transistor shape, such as gate length and gate width. Thus, it shows deviations in the same direction among chips. Global Vth variation previously has been the main challenge SRAM designers have had to overcome.

By contrast, local Vth variation is caused by fluctuation of the state of impurities in semiconductors, and arises even in adjacent transistors of the same shape. Therefore, it occurs randomly and without directivity. With the progress in transistor miniaturization, the problem of local Vth variation first manifested itself in the 90nm process generation. It is a major challenge that must be surmounted for embedded SRAM implemented in the 45nm process generation.