Top semiconductor manufacturers improve design flow through IP management

Intellectual property (IP) is used and reused as semiconductor designs

evolve from one generation to the next. IP reuse has become a necessity

since complex circuits and systems are almost always built on content

from preceding generations. IP management tools are the most efficient

way to track origins and changes, which translates into far less time

spent researching IP. Perforce Software explains how IP management tools

are already shortening design cycles while helping ensure security.

BY SIMON BUTLER, GENERAL MANAGER, METHODICS BUSINESS UNIT, PERFORCE SOFTWARE

AS IS SEEN EACH DAY, the semiconductor industry is going through a period of rapid evolution, with growing demand being counter-balanced by some considerable challenges. At the end of 2021, Perforce Software asked close to 100 industry professionals worldwide about current concerns, working methodologies, and emerging trends around design and development. While Perforce does not claim this to be an exhaustive list, the results provide valuable insight into some of the main factors shaping semiconductor design and development right now.

The largest categories of respondents were engineering management and design engineering (approximately a third each), followed by CAD management, executive management, and others. Company size ranged from under $500 million annual revenue to over $5 billion. While these organizations do vary, there are some strong areas of commonality.

The biggest industry issues

When asked about design imperatives, responding organizations’ two most important issues were time-to-market (55%) and IP reuse (45%). These point out that semiconductors are becoming commoditized, with fierce competition and slim margins in most categories. Keep in mind that even when considering more expensive application specific integrated circuits (ASICs), these designs almost always reuse at least some IP just like their commoditized cousins. Reusing some components from of a previous design — also known as IP reuse — has become a priority for many.

Respondents said the following two issues were highly important after market timing and IP reuse: functional safety (35%) and IP security (23%). In a sense this comes as no surprise, given that chips are often used in safety-critical, sensitive or highly regulated environments. Over 70% of respondents are required to meet compliance or functional safety standards, such as ISO 26262, ITAR and others, yet 70% are still using manual processes for compliance management. This may be fine for smaller teams, but this can become untenable as organizations scale. However, almost half of respondents also have some element of automated compliance management, even if it is not being used for everything.

A majority of the survey’s global respondents (76%) were also concerned about the drop in the US share of global manufacturing capacity. The hope is that the US government’s efforts to find new ways to drive more in-country manufacturing and gain more control over the semiconductor supply chain will work.

Key trends

Nearly two-thirds of respondents develop embedded software as part of their product portfolios, reflecting that the global embedded system market is predicted to grow 6.3% to $137.31 billion by 2027, according to a report published by Fior Markets1. Bundling hardware and software together creates new challenges; designs become more complex, creating a greater need for developers and designers to collaborate and manage design lifecycles in a coherent, unified way.

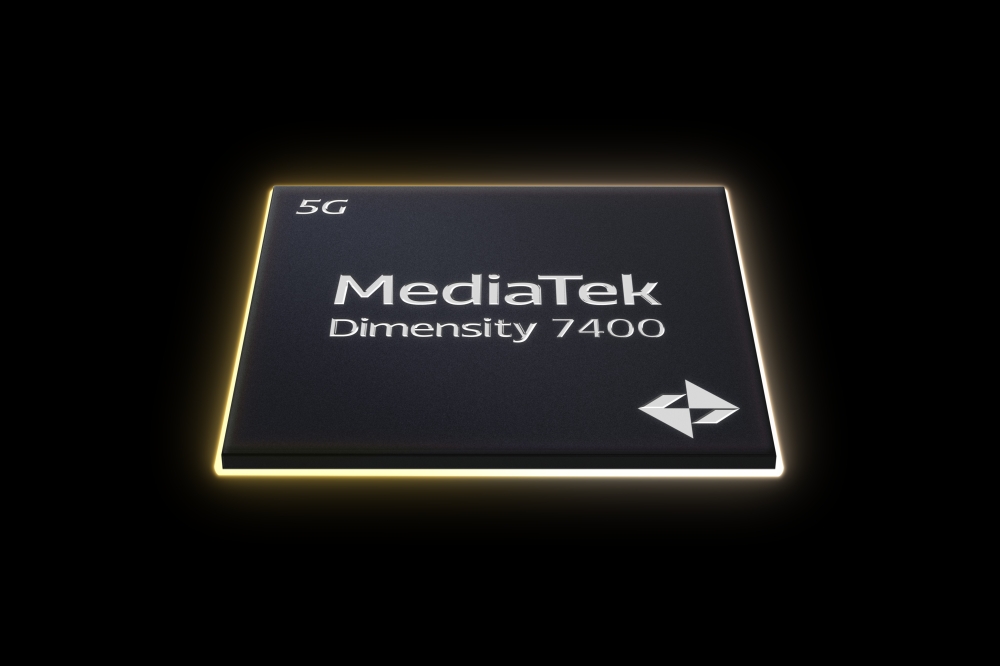

Perforce also asked about analog designs for SoCs, and almost half stated that there is 40% or more custom-IC design on a die in a typical chip in their organizations. In addition, 76% of respondents said that more than half of their jobs requires IP integration. The survey also found that 2.5D (interposer) designs are being considered or implemented by 36%. While that number may sound low, it does indicate that 2.5D is no longer being used only for expensive, high-end chips. Importantly, usage is trending upwards.

IP reuse and management are hard

While IP reuse may be a priority, many find it difficult. More than half of the respondees do not have access to a centralized IP catalog, which inhibits the design reuse discovery process. In practice, this means that people are searching through various projects or asking colleagues for recommendations. This approach is inefficient: nearly 40% report that discovering candidate IP for their designs is time-consuming and burdensome. Furthermore, for more than a third reported that trying to determine the status of IPs after making an initial discovery is a challenge, and nearly 75% reported difficulty in determining the context of an IP and its quality.

Clearly, with IP-centric design and IP reuse continuing to grow, these issues need to be addressed. Understanding the context of IPs for reuse has historically required advocates from the original project. Having a better process for identifying IP for inclusion in a project helps companies make better use of their existing assets and avoid reinventing the wheel for each new project.

Software tools can assist with these and other challenges. Perforce asked industry professionals what they were using. Over half are not using commercial IP management tools: 30% use manual tools such as Microsoft Excel, and 22% are not using any tools at all. This demonstrates that while most companies have embraced IP-centric design practices, using dedicated IP lifecycle management tools is still in its relative infancy.

However, 83% use version control software, which enables configuration management at the file level. This is a prerequisite for traceability but does not provide the necessary IP level context for component-based traceability. Component-based bills of materials (BoMs) and lifecycle management tools facilitate version control of the IP hierarchy at the individual component and system level, with dependent properties memorialized on the IP versions in the hierarchy. This allows a much richer meta-model for tracking design components and subsystems through the design lifecycle.

Requirements management tools are used by 76% of respondents. Finally, almost two-thirds use static code analysis tools, which inspect code during the development process. Both requirements management tools and static code analysis are great candidates for sourcing component level meta-data and giving IPs the context to aid reuse.

While not the majority, more of the organizations Perforce surveyed are moving to the cloud and cited reasons include optimization of capital expenditure, better pricing, support and maintenance, and control over operating costs as well as reducing the cost of expanding infrastructure. Respondents also said using the cloud helps them manage demand for peak-time computing more efficiently; it was also found to be beneficial in terms of its ease of use and access, including spinning up teams quickly and as a means to better involve home-based workers.

The big picture

Collectively, survey results paint a picture of the state of semiconductor design and development right now while offering good indicators to overcome some of the challenges that industry faces. Some things are clear: alongside ensuring IP security and compliance, dealing with the difficulties of IP management, discovery and reuse must be addressed.

As SoC designs become more prevalent with increasing amounts of the target system being developed in-house by systems companies, semiconductor development needs to take a more IP-centric approach to get ahead. The initial set of components/IPs will need to be discovered/designed, but once the base architecture is in place, good IP reuse aids design so it can become an iterative process to leverage/reuse those IPs to reduce costs and improve performance for a given system design. This partly means that finding the right platforms and tools to manage and deploy IP more effectively is key, including a common view aggregated across multiple dimensions. An IP lifecycle management (IPLM) tool can deliver significant efficiencies to the design process. It can manage many variants across different product skews, with different hardware IP and embedded software IP versions, all via a hierarchical bill of materials (BoM) overlaid with metadata to track state and quality.

Creating the right culture around IP management is equally important: as is always the case, people’s buy-in and the right processes matter as much as the supporting technology. Therefore, communicating to users the need for IP-centric design and educating them around the tools and processes required is also advised.

Worldwide, semiconductor design and development faces multiple hurdles, but likewise, there are some significant opportunities out there. The survey results underscore some of the substantial challenges and positive signs of how many organisations are focusing on IP reuse to continue thriving in this fast-changing industry.

Reference ‘Global Embedded System Market Forecast, 2020-2027’, Fior Markets, May 2020.