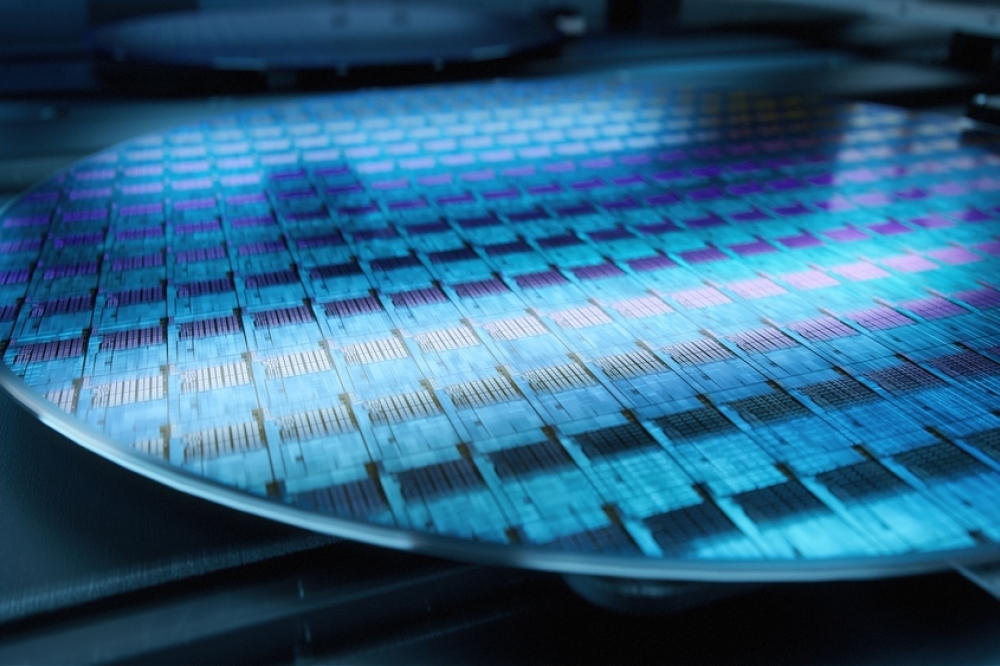

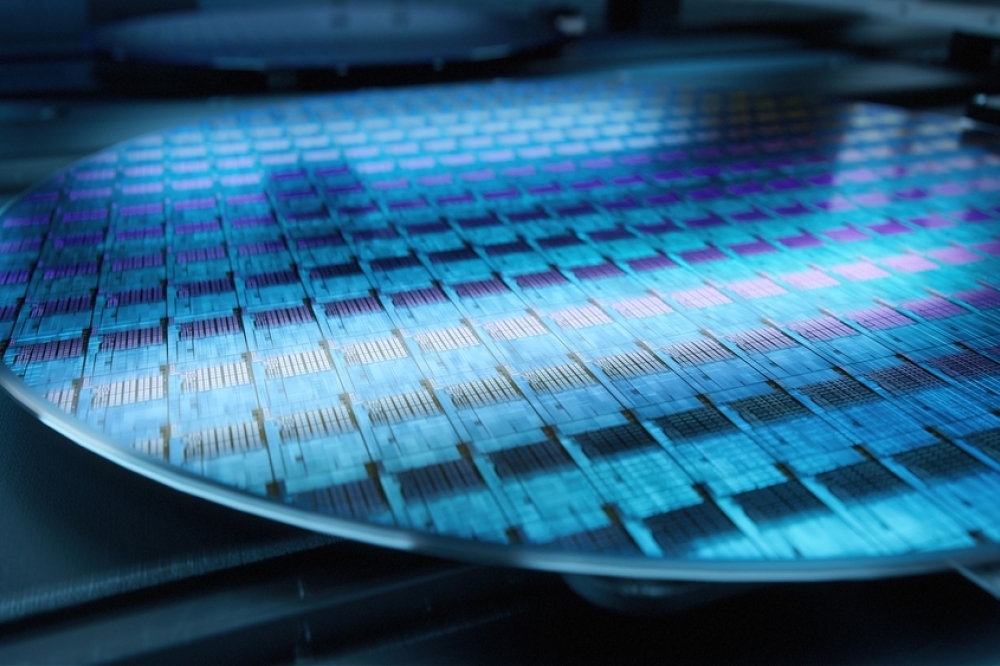

Imec demonstrates electrical yield for 20nm pitch metal lines obtained with High NA EUV single patterning

First electrical tests at 20nm pitch present a next milestone in validating the High NA extreme ultraviolet (EUV) patterning ecosystem.

This week at SPIE Advanced Lithography + Patterning, imec presents the first electrical test (e-test) results obtained on 20nm pitch metal line structures patterned after single-exposure High NA EUV lithography. Measurements on both serpentine and fork-fork metallized structures show good electrical yield, indicative of a low number of stochastic defects. The e-test results confirm the capability of the High NA EUV lithography scanner and its surrounding ecosystem to pattern lines/spaces at such a small dimension.

In August 2024, imec was the first to present industry-relevant logic and DRAM structures patterned in a single High NA EUV lithography exposure step. As a next critical step, imec shows that metallized line structures of 20nm pitch, obtained after single High NA EUV patterning using metal oxide (MOR) negative tone resist, exhibit more than 90% yield. This performance metric was obtained on two different test structures, i.e., serpentine (or meander) structures and fork-fork structures, designed to reveal information on stochastic defectivity.

Steven Scheer, senior vice president R&D at imec: “This is the first ever electrical yield demonstration of 20nm pitch metal lines obtained with single High NA EUV patterning. These results represent an initial validation of the capabilities of High NA EUV lithography and its surrounding ecosystem, including advanced resists and underlayers, photomasks, metrology techniques, (anamorphic) imaging strategies, optical proximity correction (OPC), as well as integrated patterning and etch techniques. We will continue working with our patterning ecosystem on processes to drive further yield improvement and transfer of these technologies to our manufacturing partners.”

The imec-ASML High NA EUV ecosystem includes partners such as leading chip manufacturers, material and resist suppliers, mask suppliers, and metrology experts, all working together to develop and optimize High-NA EUV lithography for next-generation semiconductor manufacturing at the sub-2 nm node.

“E-testing is a key step in High-NA EUV validation,” adds Philippe Leray, director of the advanced patterning department at imec. “These e-test results also show us the way forward. When combined with e-beam inspection, conductivity measurements of metallized serpentine and fork-fork structures give information on the stochastic defects (i.e., breaks and bridges, respectively) that lead to reduced yield. These insights support our ecosystem partners in the development of strategies to mitigate stochastic defects. One of our ongoing efforts is focused on optimizing resist performance in terms of dose-to-yield reduction with minimal impact on stochastic failures, an effort we are making in close collaboration with the resist community.”

These results will be presented in two papers at SPIE Advanced Lithography + Patterning:

Paper 13424-31 - Probing defects in metal oxide resists with an electrical yield vehicle

Paper 13424-51- Advanced PnR logic patterning enabled by high-NA EUV lithography