Interview

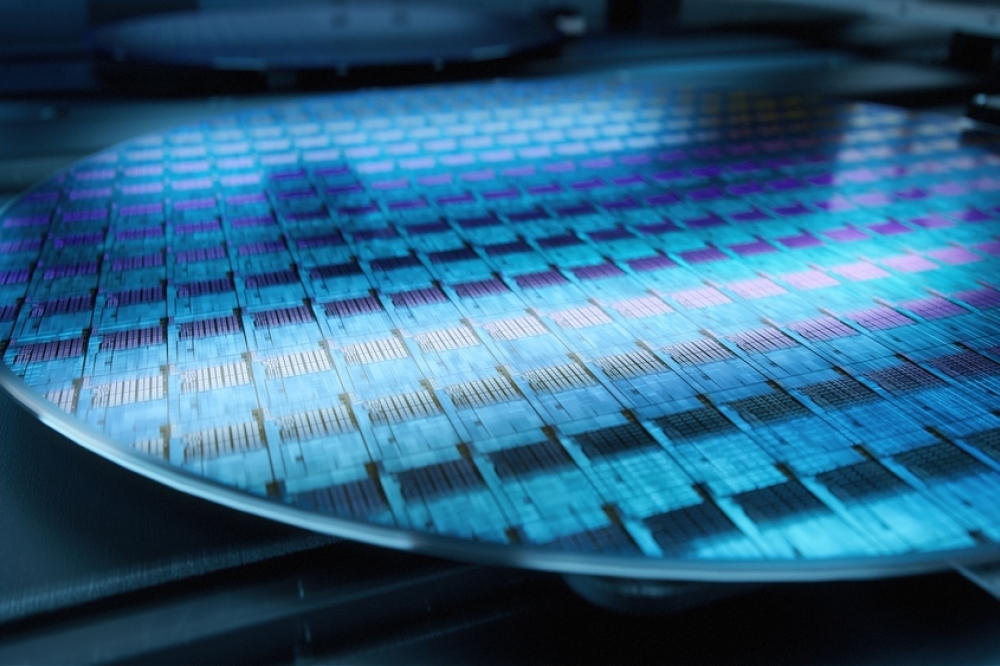

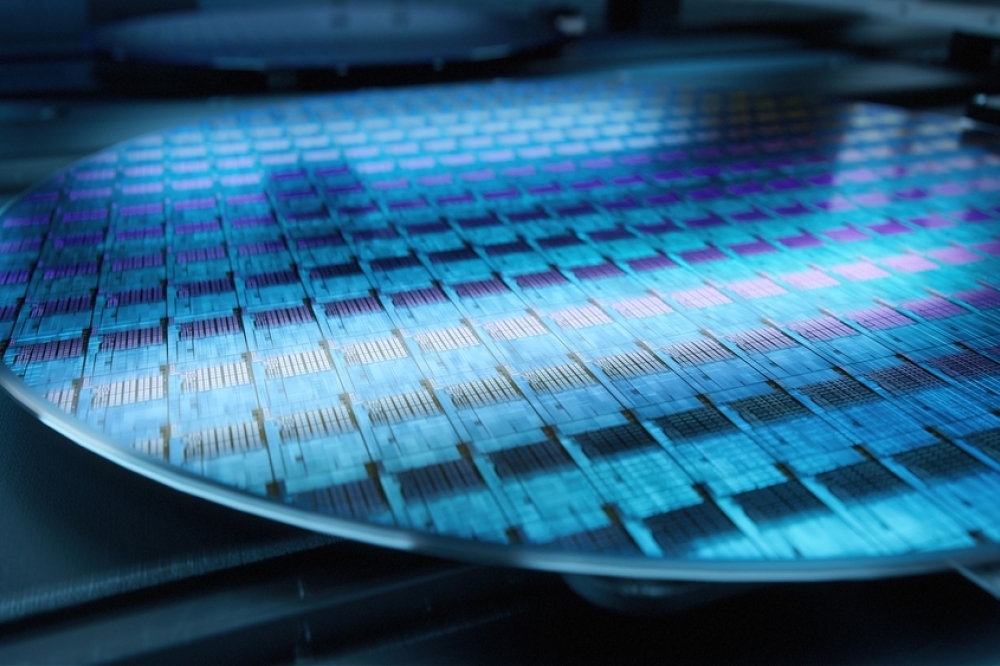

Cutting FOPLP pattern distortion

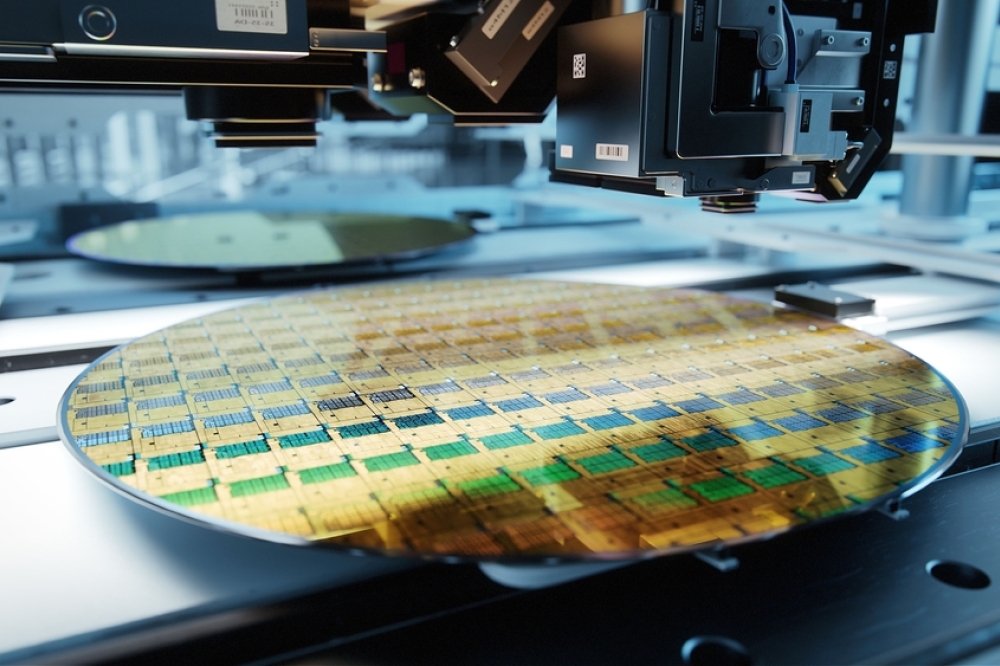

Heterogeneous integration enables multiple chips from varying Silicon processes to deliver superior performance. In large panel packages, present day limits on exposure field size forces manufacturers to ‘stitch’ together multiple reticles, which slows throughput and increases costs. Onto Innovation’s new JetStep® X500 system dramatically increases the exposure field up to 250 x 250 mm, slashing the number of exposures needed and cutting costs in FOPLP applications.

By John Chang, Corey Shay, James Webb and Timothy Chang, Onto Innovation Inc.