Saras Micro Devices participates in CHIPS National Advanced Packaging Manufacturing Program initiatives

Use of Saras’ STILETM technology strengthens U.S. semiconductor packaging advancements.

Saras Micro Devices is participating in two significant projects funded by the U.S. Department of Commerce CHIPS National Advanced Packaging Manufacturing Program (NAPMP). Each project was awarded $100 million in government funding.

The first initiative is the Substrate-based Heterogeneous Integration Enabling Leadership Demonstration for the USA (SHIELD USA) project, led by Arizona State University (ASU) and Deca Technologies, Inc. The second is the Substrate and Materials Advanced Research and Technology (SMART) Packaging Program, led by Absolics, Inc. Saras will contribute its STILE™ product technology to both projects to enhance device package integration of advanced power delivery solutions for high-performance computing (HPC) and artificial intelligence (AI) applications.

"Saras’ STILE technology enhances our substrate efforts," said Jason Conrad, chief operating officer of ASU’s Southwest Advanced Prototyping (SWAP) Hub and site lead for MacroTechnology Works. "It adds functionality that complements our core development goals, helping to further elevate the capabilities of the advanced packaging solutions we’re developing."

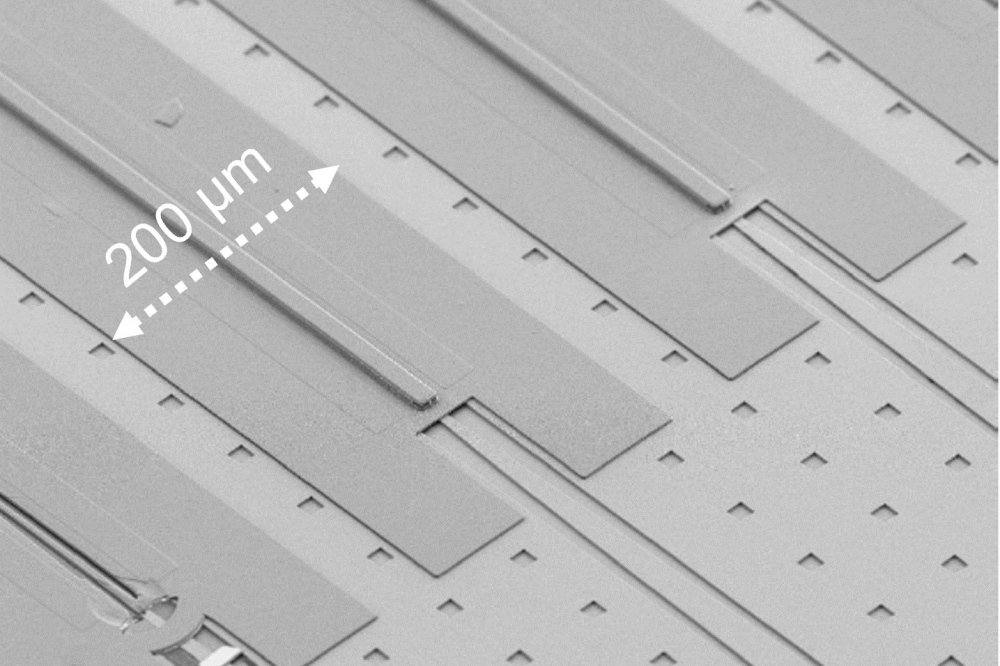

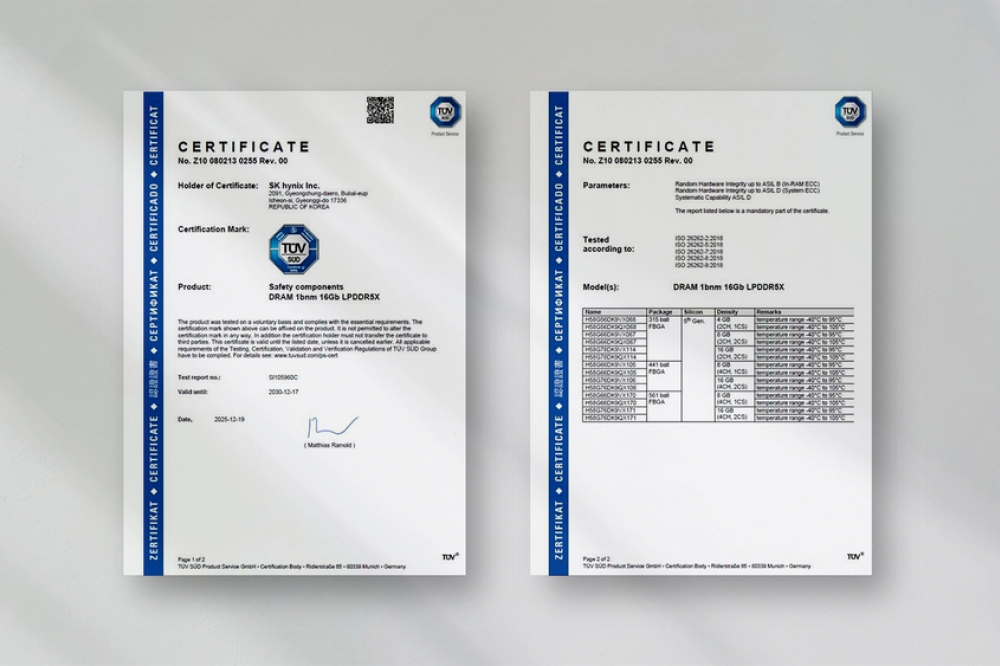

Over the past year, Saras has secured seven foundational patents for its capacitor and STILE technologies from the United States Patent Trademark Office. This achievement underscores the company’s commitment to innovating critical solutions in power delivery for next-generation AI and HPC devices.

“The power delivery challenges posed by AI require innovative solutions,” said Ron Huemoeller, CEO of Saras. “Our STILE technology addresses these challenges by enabling in-package power delivery close to the source, improving both efficiency and performance while opening up package real estate for higher levels of chiplet integration.

By collaborating on the SHIELD USA and SMART projects, we’re able to contribute critical AI power delivery elements and, consequently, significantly advance U.S. semiconductor manufacturing capabilities.”

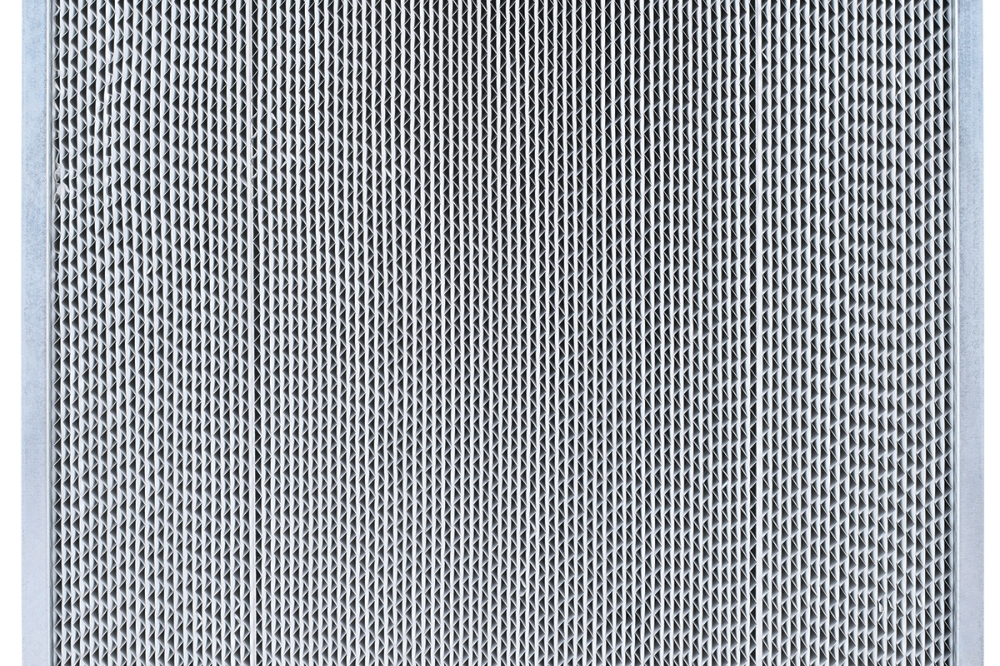

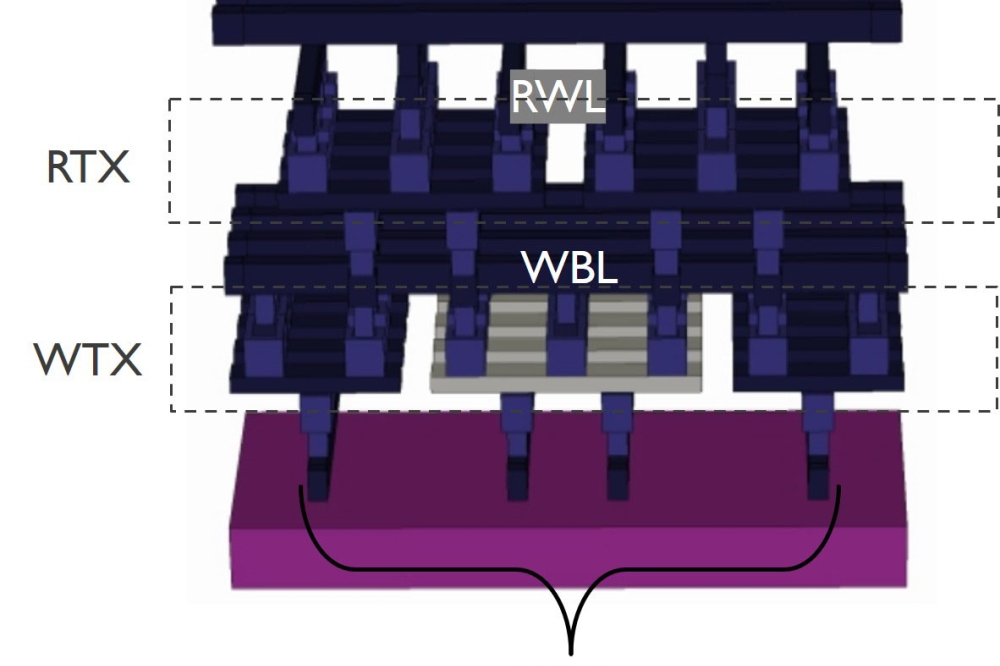

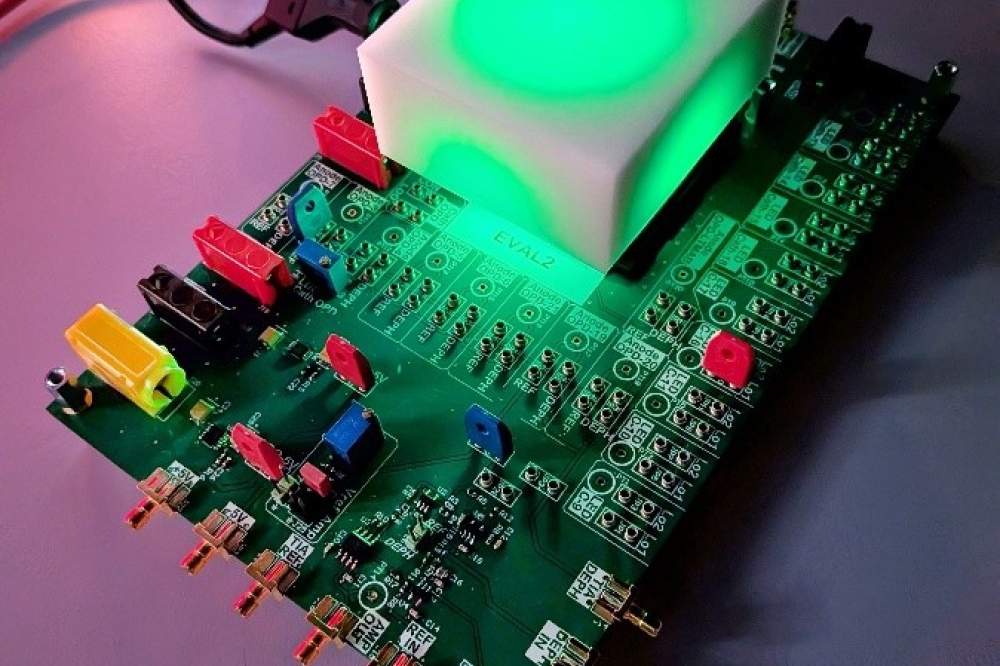

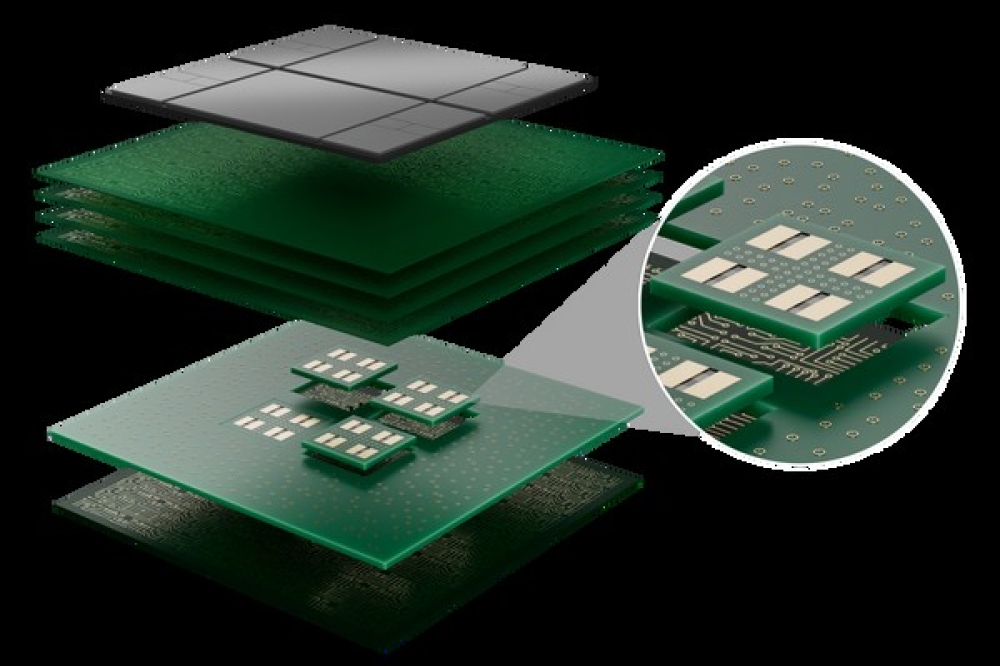

STILE introduces a multi-domain, integrated passive module that embeds directly into the substrate core of device packages. This approach reduces the need for multiple function-specific devices, maximizes packaging real estate by optimizing space, and supports higher levels of chiplet integration—essential for the demands of AI workloads.

The technology aligns with the goals of the NAPMP projects and will extend the advanced substrate technology solutions that the SHIELD USA project and SMART Packaging Program are focused on delivering.

“This joint effort exemplifies how integrating complementary innovations can drive advancements in semiconductor packaging and address the performance demands of AI and HPC applications," stated Craig Bishop, CTO of Deca Technologies. "SHIELD is truly a collaborative effort, combining Saras’ embedded passive technology with Deca’s novel interconnects at ASU's research fab to demonstrate leap-ahead organic substrates."

The collaborations under the NAPMP advanced substrate and material projects highlight the importance of innovative power delivery solutions in maintaining U.S. leadership in semiconductor technology. By developing and scaling advanced packaging processes, materials, and equipment, these initiatives aim to create a robust foundation for high-volume semiconductor packaging production in the United States, enhancing national security and economic resilience.