System level test enables a paradigm shift for device manufacturers

According to research conducted by AEM Singapore, the semiconductor industry needs continuously improved faults coverage while reducing the overall costs of test and measurement operations to enable better, more efficient defects detection while improving quality and overall yield.

BY STUART PEARCE, AEM HOLDINGS, SINGAPORE

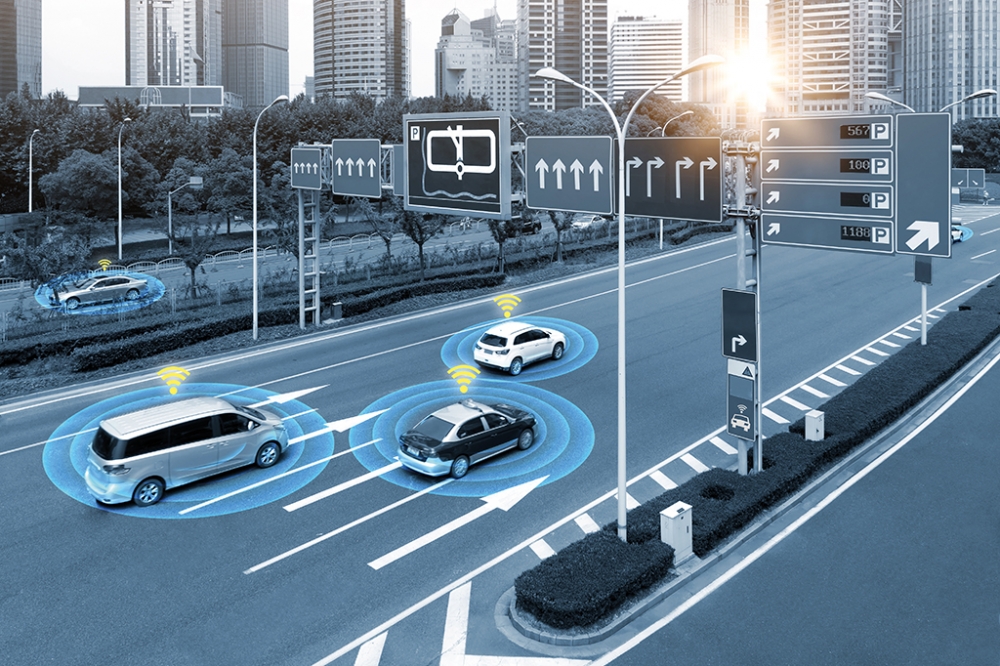

FAULTS COVERAGE is becoming more problematic as systems are getting more complex, heterogeneous and applications are more demanding. Applications such as self-driving cars, cloud servers, AI, industrial IOT or medical devices are now mission critical to many end use sectors, driving the need for low parts per billion (PPB) defect levels.

Advanced Driver Assistance Systems (ADAS) and infotainment applications

Semiconductors continue to follow Moore’s Law regarding the doubling of transistors at every process node. While these leaps occurred previously in 18-24 month periods, the complexity of advanced nodes has made progress more challenging and time between nodes greater. As these new process nodes come to market, higher numbers of smaller transistors will make it more difficult to catch defects, and will make test coverage more demanding.

Figure 1: As on-board automotive systems rely more heavily on semiconductor based system, the requirement for fast, accurate and cost-effective testing increases

For example, test coverage of 99.4% of an advanced node 300mm wafer still leaves 15 million transistors untested on a 2.5 billion transistor device. Time to market and time to revenue drives the need for shorter cycle time with increased faults coverage. System level test in the customer application environment provides the ability to solve these challenges while providing an opportunity to significantly reduce overall cost of test.

A New System Level Test Solution (AMPS)

AEM Singapore has developed a new system level test solution (AMPS) that leverages the knowledge and experience gained over the last decade in system level device handling for leading semiconductor companies. AMPS stands for Asynchronous, Modular Parallel and Smart as key parameters for system level testing.

System level testers need to be modular and also be easily customized and reconfigured as required for specific device applications. Working with customers to integrate their modified application evaluation module into a system test handling solution leverages the existing test development.

Figure 2: As transistor sizes decrease, more devices are squeezed into each wafer, creating complex test environments. Source: Qualcomm Mike Campbell

Providing a modular approach that can be replicated and scaled enables the same system to be used in engineering debug environments with the key advantage being that the system a development team initially worked with can be ramped in production. Such production oriented solutions need to be completely asynchronous in operation to enable each system evaluation board to be essentially ‘stand-alone’ in operation. This facilitates the ability to reconfigure systems without taking a line down and enables individual smart device test flows.

Figure 3: Example of a testing scenario

Modularity by re-using the same components enables scalability for massively parallel test handlers, which can reduce the overall cost of ownership. The AEM System Tester (AMPS) is scalable to the point that it can handle individual devices for engineering debug up to 480 parallel sites. It offers individual device ATC thermal control from -40C up to 150C, supporting burn-in and stress test within the same system. Adding optional system level functional test capability (SLT+) enables BIST, MBIST and functional testing within the same system. This provides the ability to configure a system for multiple different devices or modules to be tested at the same time supporting applications with a higher mix of products such as those frequently offered by OSAT manufacturers

Figure 4: The AEM System Tester (AMPS)]]

Test flow with system level test

Collecting system level test data enables correlation back to both functional test and wafer test results. By accessing stored data, analytic systems can enable smart knowledge based adaptive test decisions to be made between wafer, functional and system level test (SLT), which can further reduce the overall cost of test. Adding optional functional test modules at the system level further enables adaptability within the same system.

Advances in data analytics, machine learning and massive parallel test handling systems are now enabling a shift in testing paradigm. System level testing is not a new concept, but is now proven and ready to help increase faults coverage while reducing the overall cost of test.