DARPA invests $2.9 million in cooling silicon chips

Researchers from the Georgia Institute of Technology have won a Defence Advanced Research Projects Agency (DARPA) contract to develop three-dimensional chip-cooling technology.

The scientists say this development will enable silicon chips to handle heat loads as much as ten times greater than systems commonly used today.

In addition to higher overall chip heat dissipation demands, the new approach will also have to handle on-chip hot-spots that dissipate considerably more power per unit area than the remainder of the device. Such cooling demands may be needed for future generations of high-performance integrated circuits embedded in a wide range of military equipment.

"There is really no good way to address this heat dissipation need with existing technology, and the problem is getting worse because computing power is increasing and the capabilities being put on chips are expanding," says Yogendra Joshi, a professor in Georgia Tech's Woodruff School of Mechanical Engineering and the project's principal investigator.

"There is a real need for developing schemes that can address high power on the whole chip coupled with very high power dissipation areas that are only a few millimetres square," he adds.

DARPA's Microsystems Technology Office, which provided the three-year $2.9 million contract, is seeking techniques to dissipate heat of as much as one kilowatt per square centimetre in the overall integrated circuit, and five kilowatts per square centimetre on smaller areas. The research is part of DARPA's Intrachip/Interchip Enhanced Cooling (ICECool) program.

"The approaches that we are talking about are relatively high-risk," notes Joshi, who specialises in electronic cooling from the chip-level on up to full-sized data centres. "They have not been tried before, so there are real questions of reliability "“ whether they can hold up under repeated cycles of being powered up and powered down."

In addition to Joshi, the research team includes:

Muhannad Bakir, an associate professor in the Georgia Tech School of Electrical and Computer Engineering, who specialises in three-dimensional interconnected systems;

Andrei Fedorov, a professor in the Georgia Tech School of Mechanical Engineering, who specializes in understanding and utilising unique physical properties at the nanoscale, and

Suresh Sitaraman, also a professor in the Georgia Tech School of Mechanical Engineering, who specializes in evaluating electronic device reliability through innovative characterization techniques and physics-based modelling.

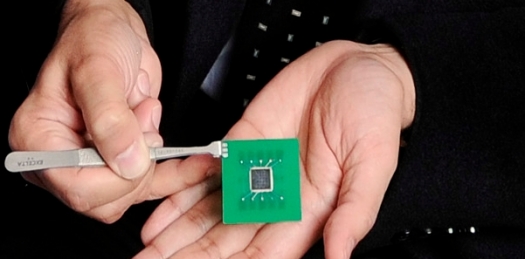

Georgia Tech researchers Muhannad Bakir, Andrei Fedorov, Yogendra Joshi and Suresh Sitaraman are developing three-dimensional chip cooling technology that will be able to handle heat loads as much as ten times greater than systems commonly used today. (Georgia Tech Photo: Gary Meek)

While applications for the high-powered chips aren't specified, their installation in systems intended for field use will add to the level of challenge.

"For speed and performance issues, this computing power may be embedded where it is needed in the field," Joshi adds. "The challenges of cooling these high performance integrated circuits will be even more challenging because they will operate in environments that may be adverse compared to an office or computer room situation."

There are a number of significant challenges ahead.

The first is in implementing non-uniform cooling using liquid evaporation in three dimensional integrated circuits. The program calls for two dies to be cooled together, but the approaches developed for that could be used in multiple stacked dies. Being able to cool smaller areas with higher heat dissipation needs will provide an additional challenge.

Also, meeting reliability standards whilst ensuring that the coolant and vaporisation within tiny microfluidic passages does not induce liquid dry-out, passage cracking, fluid leakage or undesirable electronic performance is needed.

Finally, fabricating micron-scale cooling structures smaller than the thickness of a hair in the integrated circuit stack and understanding the flow and heat transfer physics taking place at that scale is another of the aims.

"It is well known that cooling constraints play a critical role in designing electronic systems," says Bakir. He adds, "Often a favourable electronic system configuration may not be realizable due to lack of adequate cooling. The novel microscale thermal technologies that will result from this project will address the most demanding thermal needs of future heterogeneous 3-D nanoelectronic systems and will enable new levels of performance and energy efficiency."

Beyond the technology challenges, the researchers will also need to develop a detailed and fundamental understanding of how liquids boil at the micron size scale.

"The physics of how liquids boil has been well studied for large systems such as power plant boilers," Joshi notes. "What we are talking about here is boiling that will take place in passages that are produced by microfabrication techniques that may be only 50 micrometres by 50 micrometres. The physics of what will be going on there is very different than what happens at the large scale, and how these liquids boil in the passages of interest will result in new scientific insights."

Selecting an appropriate coolant able to provide the necessary phase change performance, while not damaging the silicon chips, will be part of the project. In an earlier research program supported by the Office of Naval Research, Georgia Tech developed new coolant candidates that will be considered along with traditional dielectric fluids.

The research will be done in collaboration with industry partner Rockwell-Collins, a major manufacturer of electronic systems for the military. That collaboration will help ensure that solutions developed will be compatible with defence system requirements.

"The challenges for material characterization and physics-based modelling are to consider the larger features of the electronic system without overlooking the micrometer and sub-micrometre scale features that are the main locations for fracture and failure," says Sitaraman. "Mechanical characterisation and physics-based modelling will be important to understanding the reliability of microelectronic systems operating with fluid passages."

Beyond meeting the project requirements, the research will produce technology advances that should be broadly useful for future microsystems.

"The technologies we have proposed aim to explore uncharted territory in multiple science and technology domains to bring about an order-of-magnitude improvement in the current state-of-the-art," says Fedorov. "The project represents a significant challenge on the most fundamental level of materials and fluid behaviour down to the sub-micron scale. We're confident that this project will produce some really new technologies to address the needs of future 3-D microsystems."

This research is supported by DARPA under contract HR0011-13-2-0008.