Tektronix enables real-time DDRX memory analysis

MCA4000 provides instantaneous visibility into memory interfaces over long analysis runs for deep insight into memory bus activity

Tektronix has announced the availability of real-time memory execution validation capabilities for faster protocol, performance and compliance analysis of JEDEC DDR4, DDR3 and DDR3L memory standards.

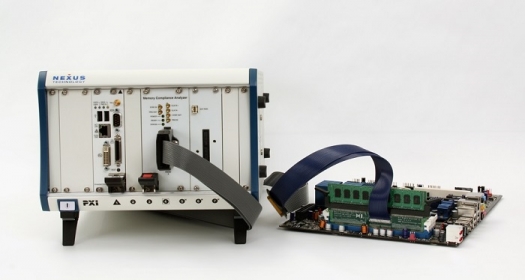

The MCA4000 protocol compliance and bus protocol analyser developed by Nexus Technology, a Tektronix partner for memory solutions, enables the instantaneous observation of memory interfaces over long periods of time, providing deep insight into memory bus activity that can help to shorten debug cycles and speed time to market.

As the industry transitions to new memory technologies like DDR4 and DDR3L with higher data rate, lower power consumption and greater capacity, designers face new challenges to validate and debug devices with tighter margins, faster edge rates and complex bus protocols.

With the addition of real-time execution validation capabilities, Tektronix meets these demanding requirements with the industry's most complete memory analysis portfolio, which includes existing solutions for electrical test and logic debug along with a broad family of probes, interposers and software analysis capabilities.

"The latest JEDEC standards make memory validation and debug a far tougher and more demanding task than it has ever been in the past," says Brian Reich, general manager, Performance Oscilloscopes, Tektronix. "Execution validation completes our portfolio to give customers the broad range of test solutions they need to quickly isolate problems and debug all types of memory regardless of speed or form factor."

The MCA4000 memory compliance analyser features a dual architecture that enables the detection of protocol violations coupled with the ability to acquire and analyse violations and determine bus performance. The MCA4000 has an integrated protocol analyser that monitors a DDR memory bus at-speed, reporting statistical results on events and violations in real-time. It also has an integrated, full function logic analyser with 1G cycle acquisition depth.

The instrument incorporates a fully programmable front-end that provides the ability to generate oscilloscope-like eye diagrams to graphically illustrate DDR PHY settings, bus integrity and required sample points. The Tektronix family of probes and interposers are shared between Tektronix 7000 series logic analysers and the MCA4000, providing the ability to view high speed timing, state, protocol and real-time analysis data simultaneously with one single load.

The MCA4000 is available now worldwide.